## Nanowire Modeling & Design Technical Report

Aidan Prendergast, Claire Ryan Hagar, Imtiaz Ahmed

[ajprende@purdue.edu](mailto:ajprende@purdue.edu), [ryan253@purdue.edu](mailto:ryan253@purdue.edu),

[ahmed202@purdue.edu](mailto:ahmed202@purdue.edu)

School of Electrical and

Computer Engineering

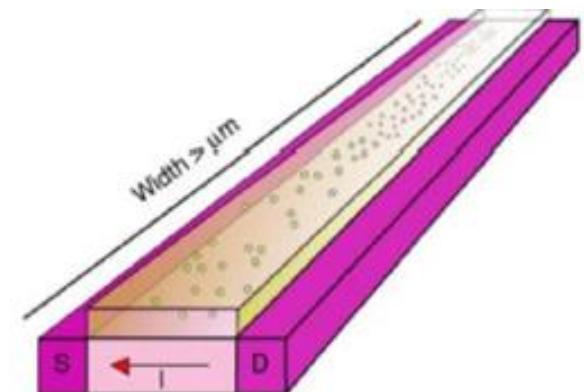

- Traditional Planar MOSFET faces several challenges as device dimensions are scaled down.

- Increased Short channel effects

- Increased Leakage Currents

- Deteriorating On/Off Current ratio and Subthreshold Swing

- Drain-Induced-Barrier-Lowering (DIBL): Drain gets control over Channel conduction

- Continuing Moore's Law—the trend of doubling transistor density approximately every two years- thus becomes more difficult

- Nanowire Transistors provide a nifty way to alleviate these challenges

Traditional

Planar MOSFET

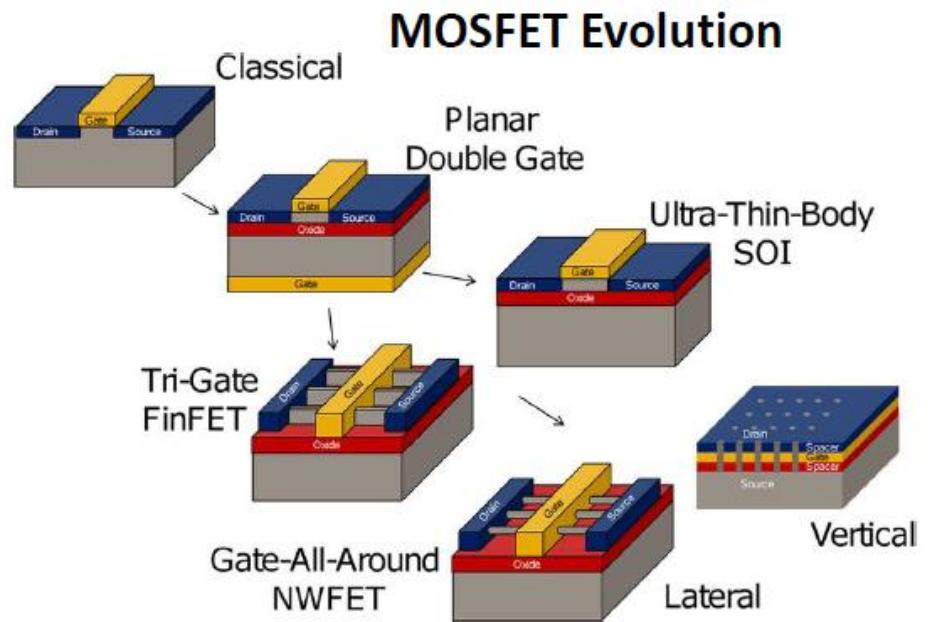

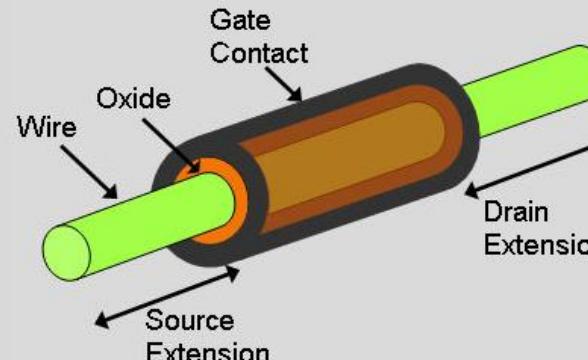

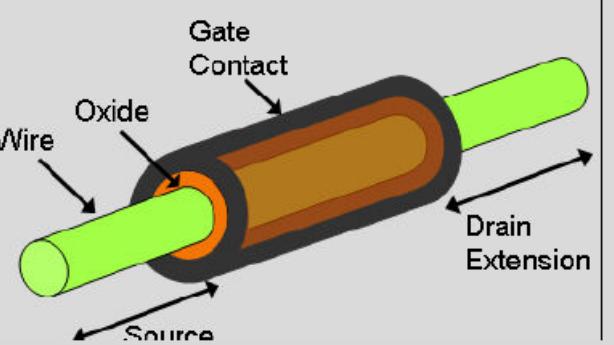

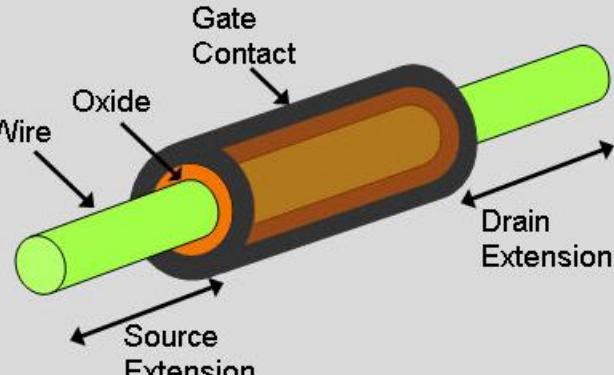

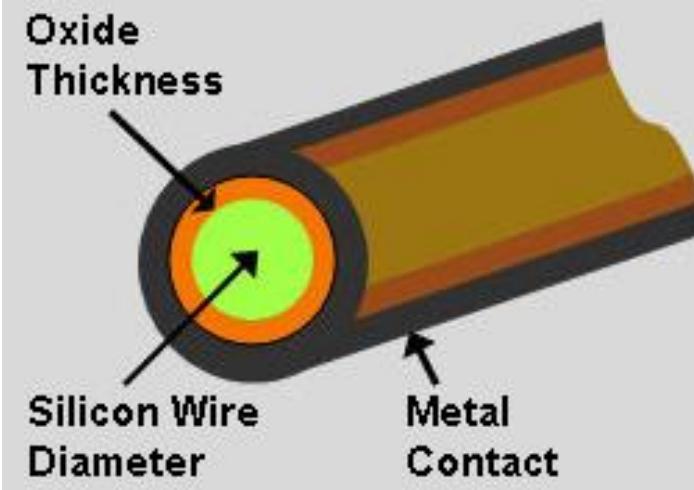

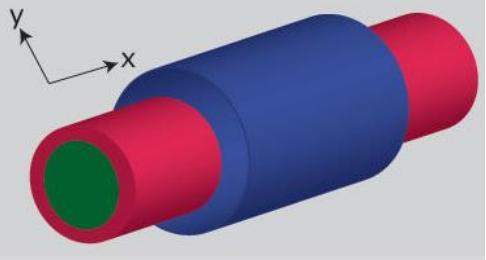

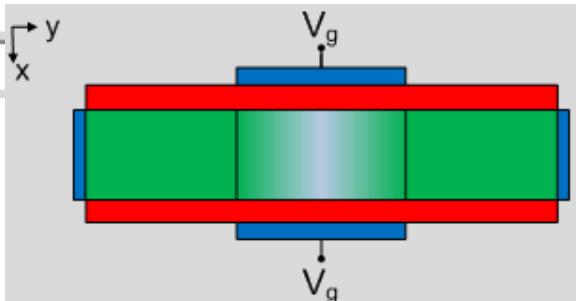

## Nanowire Transistors:

- Gate surrounds Channel

- Provides greater Gate control over channel conduction leading to

- higher switching speeds

- lower power consumption

- improved overall performance in terms of On/Off Current ratio and Subthreshold Swing

## Goal of this Project:

- Analysis and Comparison of Gate scaling effects in Planar and Nanowire MOSFET

- Analysis of Classical (Drift-Diffusion), Semi-classical (Top-of-the-barrier), and Quantum Transport models of Nanowires

- Exploration of electron and hole nanowire characteristics

# Classical MOSFET Limitations (Quad Chart 1 of 2)

## Objective:

- Understand the various physical effects when scaling the gate length of a MOSFET.

## Problem:

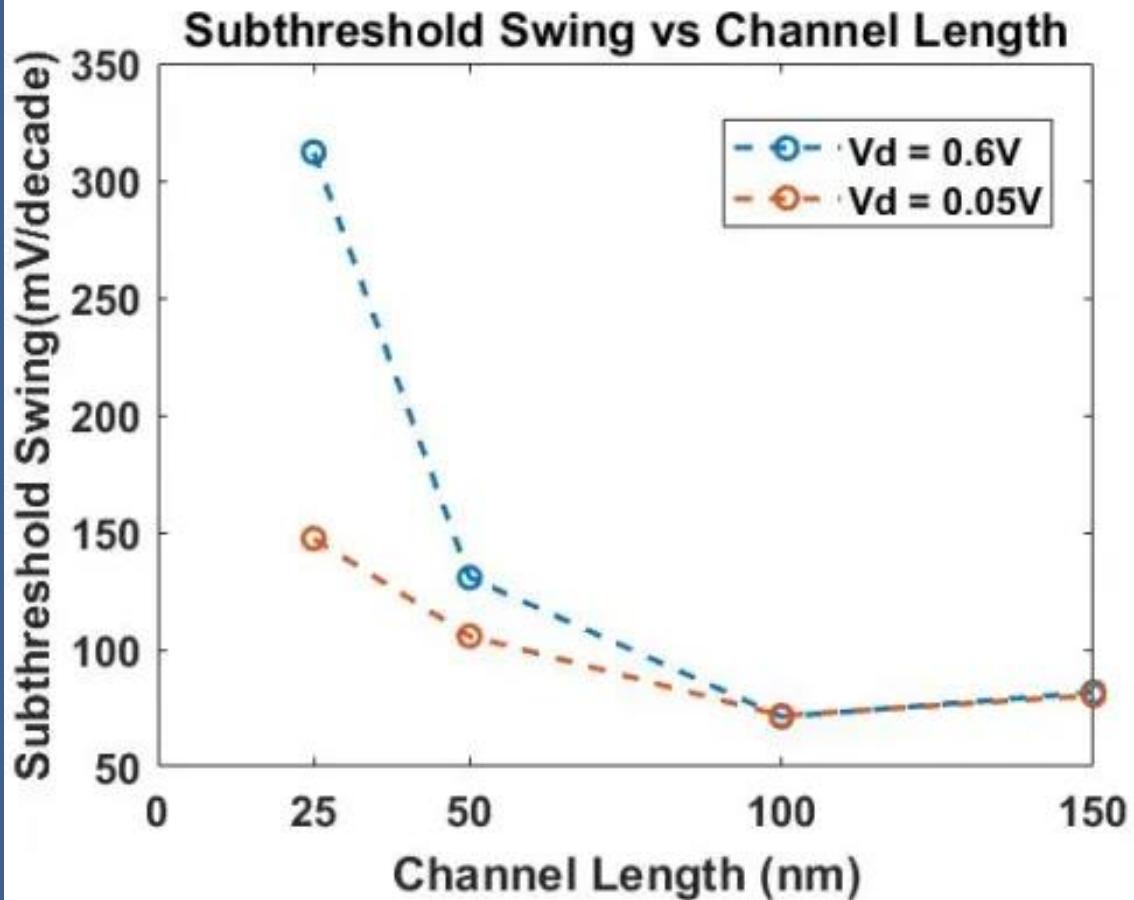

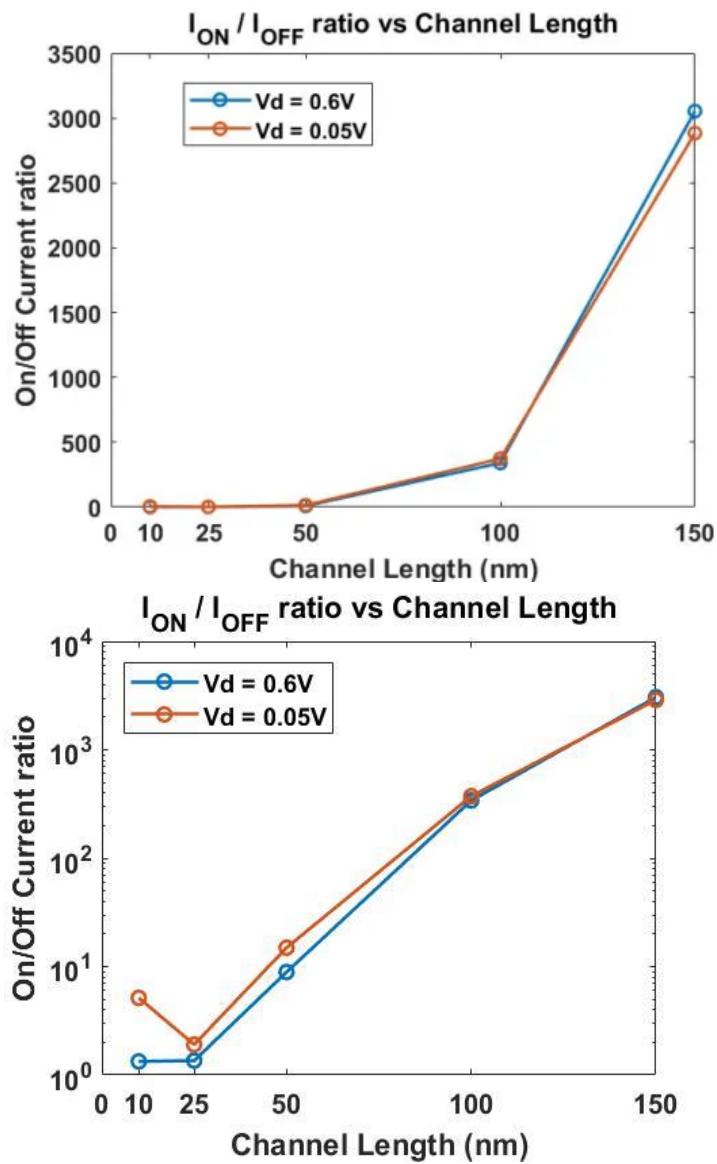

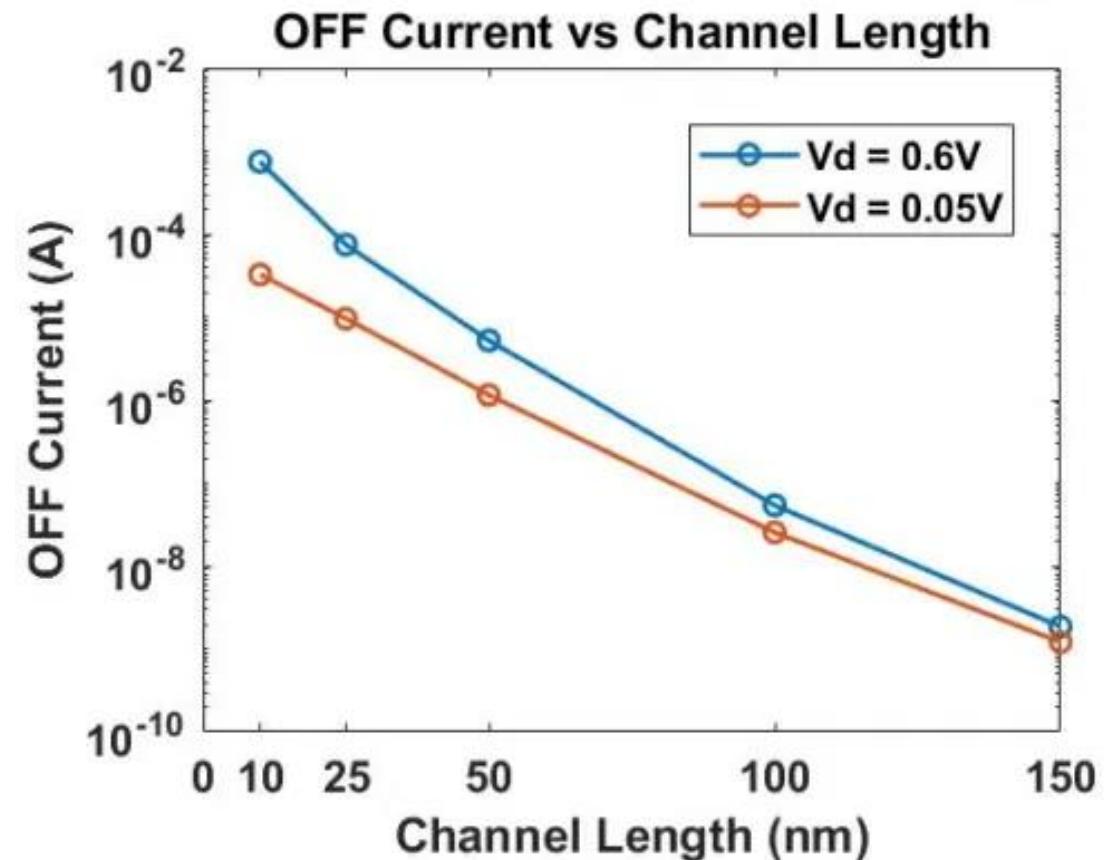

- The ON/OFF current ratio, a large ON current, and the subthreshold swing can all be affected from the gate length.

## Results / Impact:

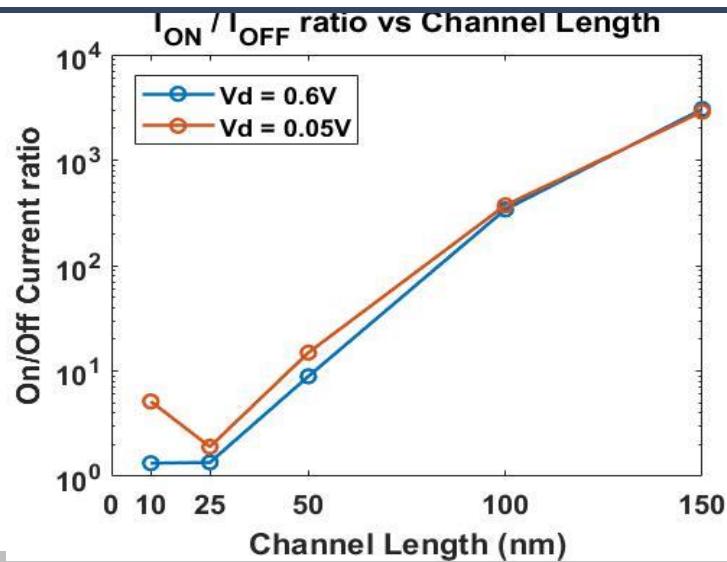

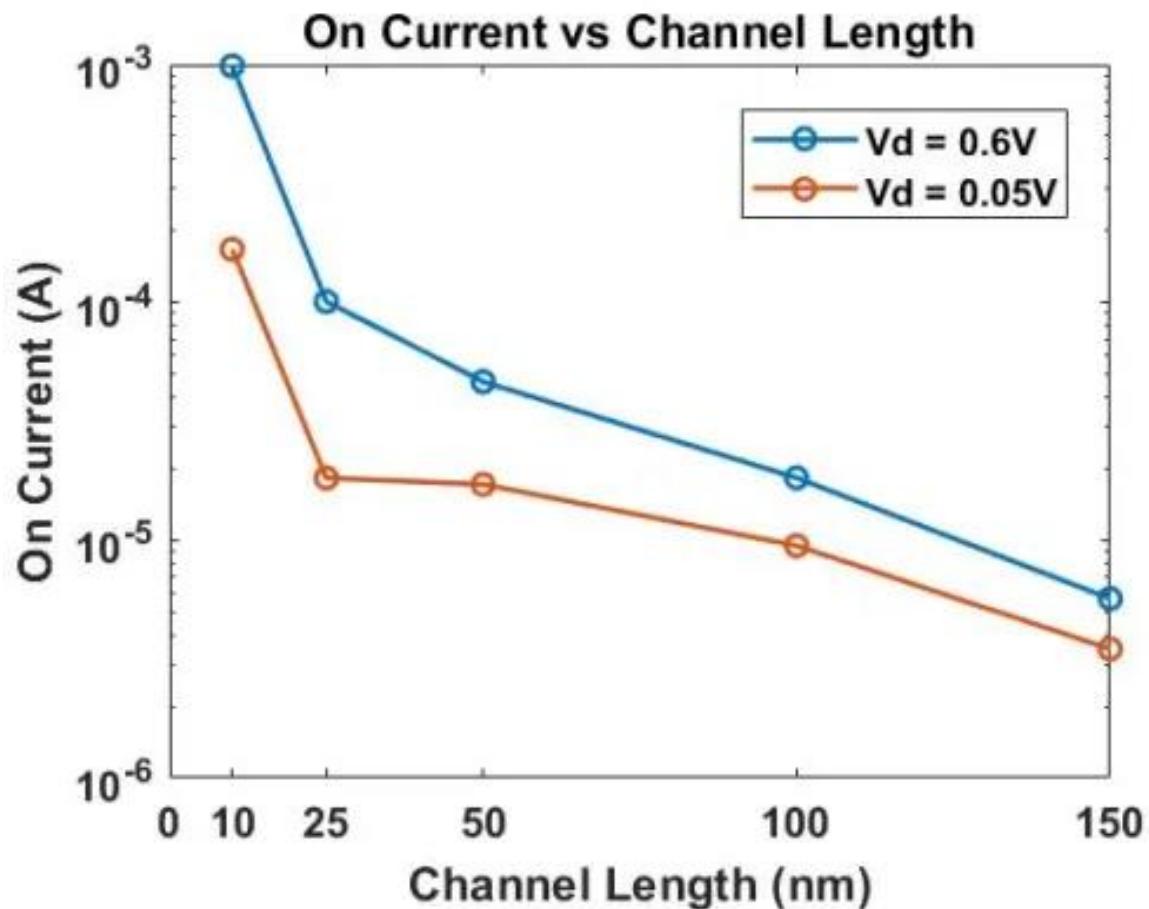

- The ON/OFF current ratio increases as the channel length increase: inverse relationship to subthreshold swing. Also, On Current and Off Current decrease as channel length increases.

- The ON/OFF current ratio is shown below. Others are shown in the Appendix ([Transistor Features](#)).

- As we scale the device down, Leakage currents become significant, resulting in high OFF currents and thus deteriorated device performance.

## Approach:

- An n-type MOSFET was modeled in NanoHub's MOSFET, varying the gate length from 150nm to 5nm.

- Please see [NanoHub MOSFET Inputs](#) (located in the Appendix) for the inputs used in this simulation.

# Classical MOSFET Limitations (Quad Chart 2 of 2)

## Objective:

- Understand the design changes that can and have been made to increase transistor performance.

## Problem:

- Various characteristics can be changed to affect the transistor performance.

## Approach:

- An n-type MOSFET was modeled in NanoHub's MOSFET, varying the gate length from 150nm to 5nm.

- Please see [NanoHub MOSFET Inputs](#) (located in the Appendix) for the inputs used in this simulation.

## Results / Impact:

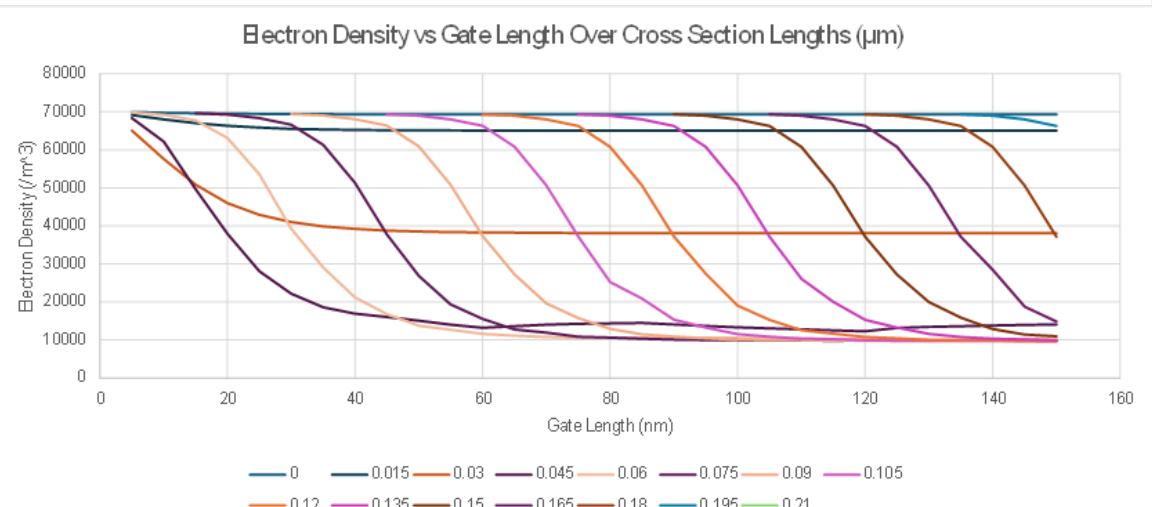

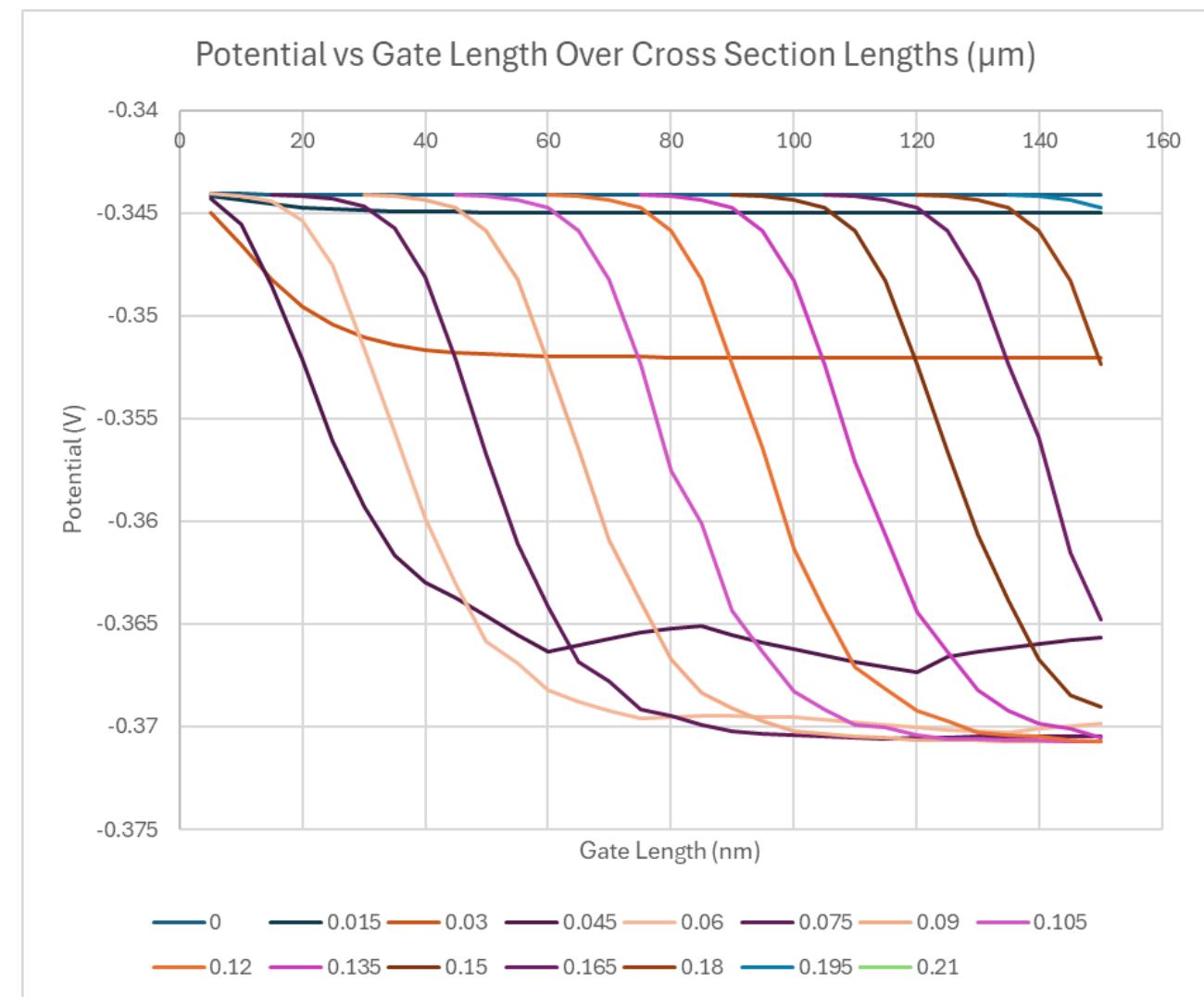

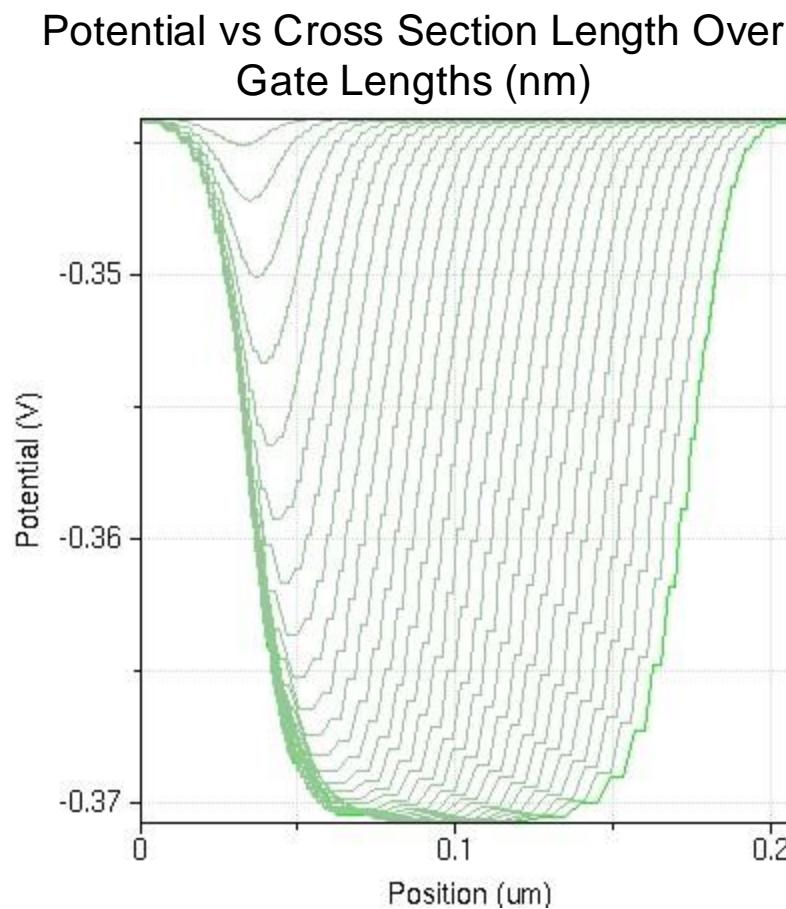

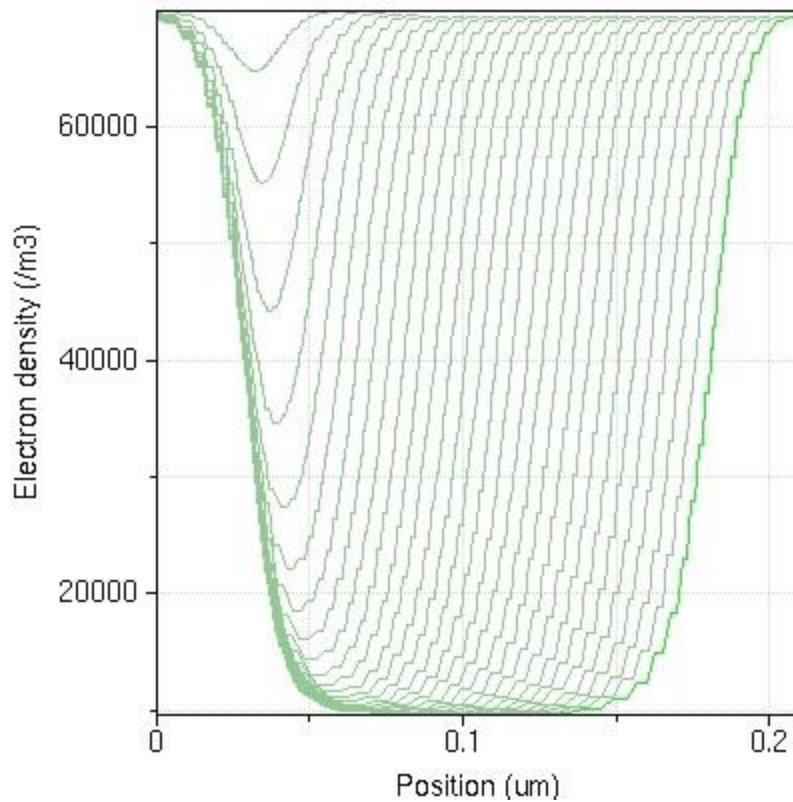

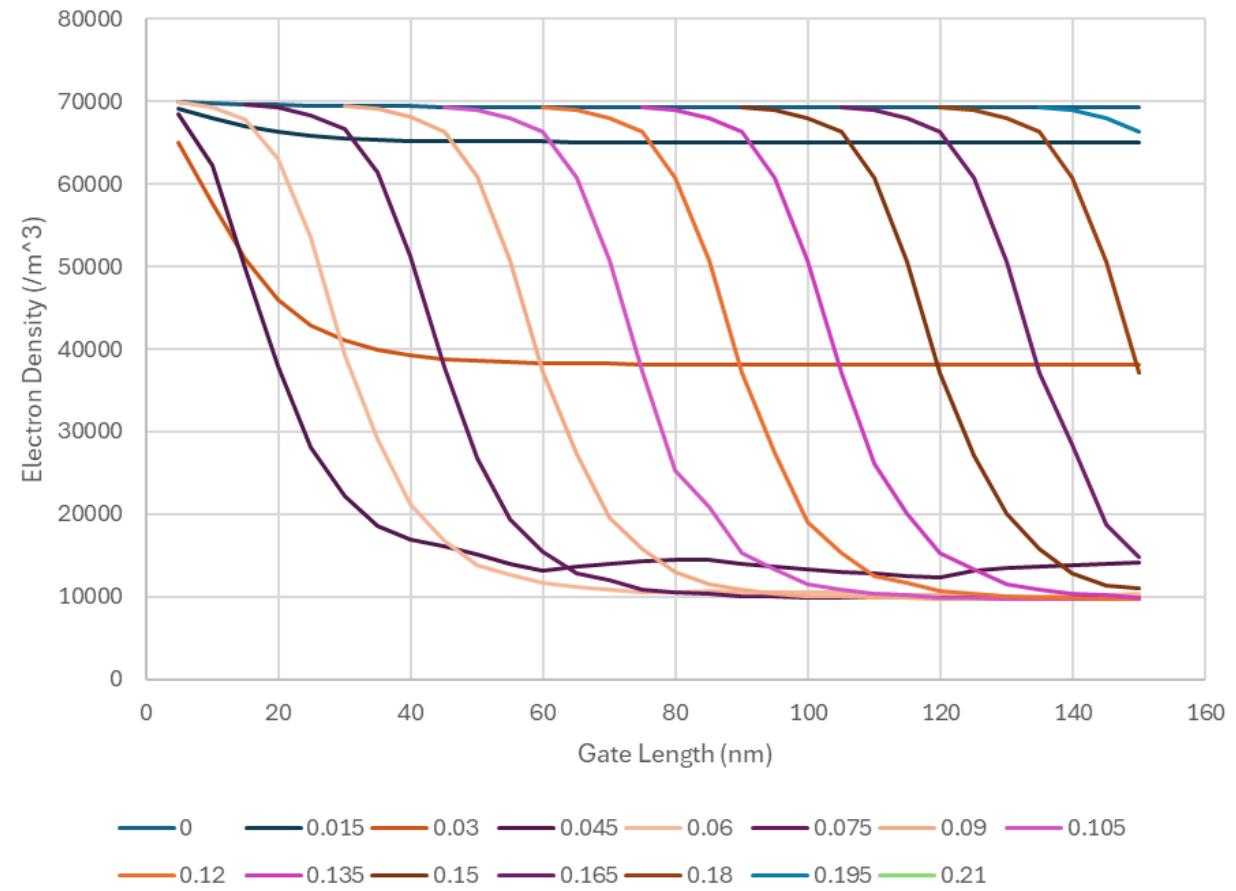

- Both the voltage potential and electron density is decreased with an increase of gate length.

- The relationship of electron density and gate lengths is shown below. Please see [Voltage Potentials](#) (located in the Appendix) for the relationship of voltage potential.

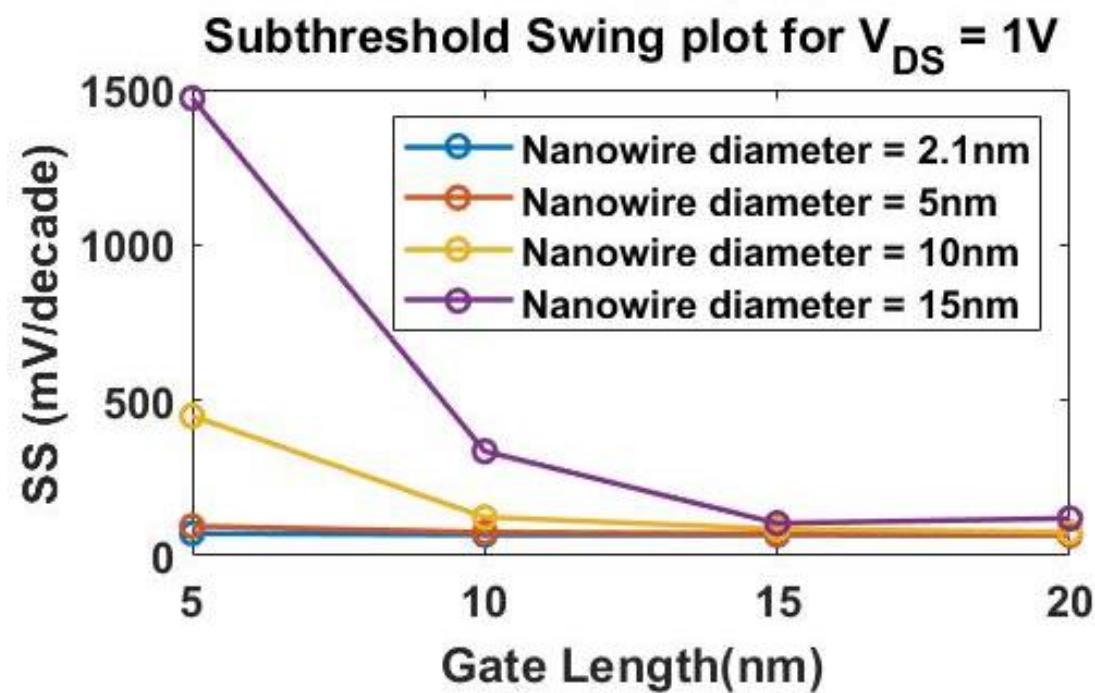

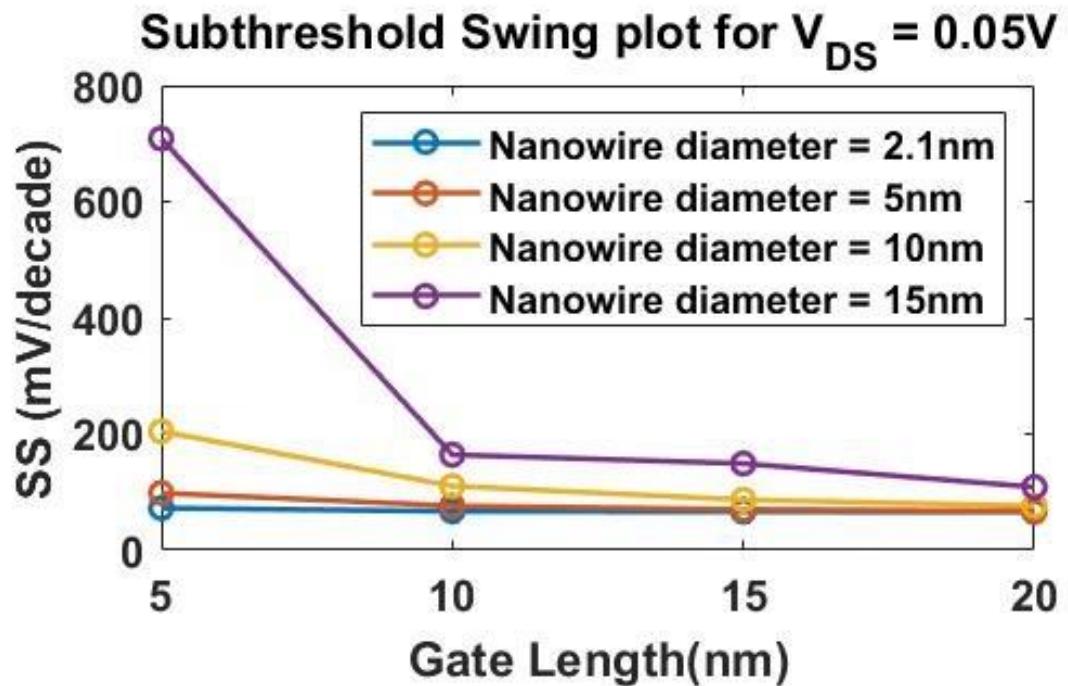

# Nanowire with Drift Diffusion (Quad Chart 1 of 2)

## Objective:

- Understand how critical transistor parameters respond to the scaling of the gate length and nanowire diameter.

## Problem:

- The ON/OFF current ratio, threshold voltage, and subthreshold swing can all be impacted by changing parameters.

## Approach:

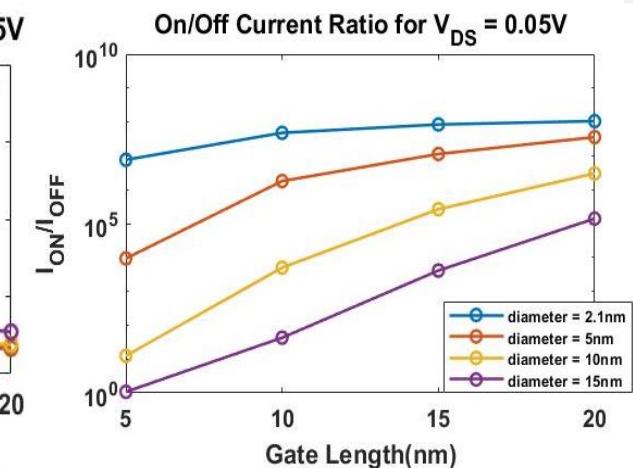

- NanoHub's NANOFINFET tool was used to simulate device performance while varying the nanowire diameter and gate length.

- Please see [NANOFINFET Inputs](#) (located in the Appendix) for the inputs used in this simulation.

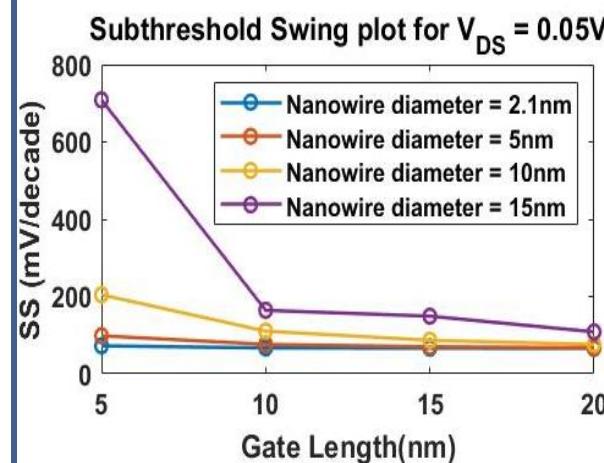

## Results / Impact:

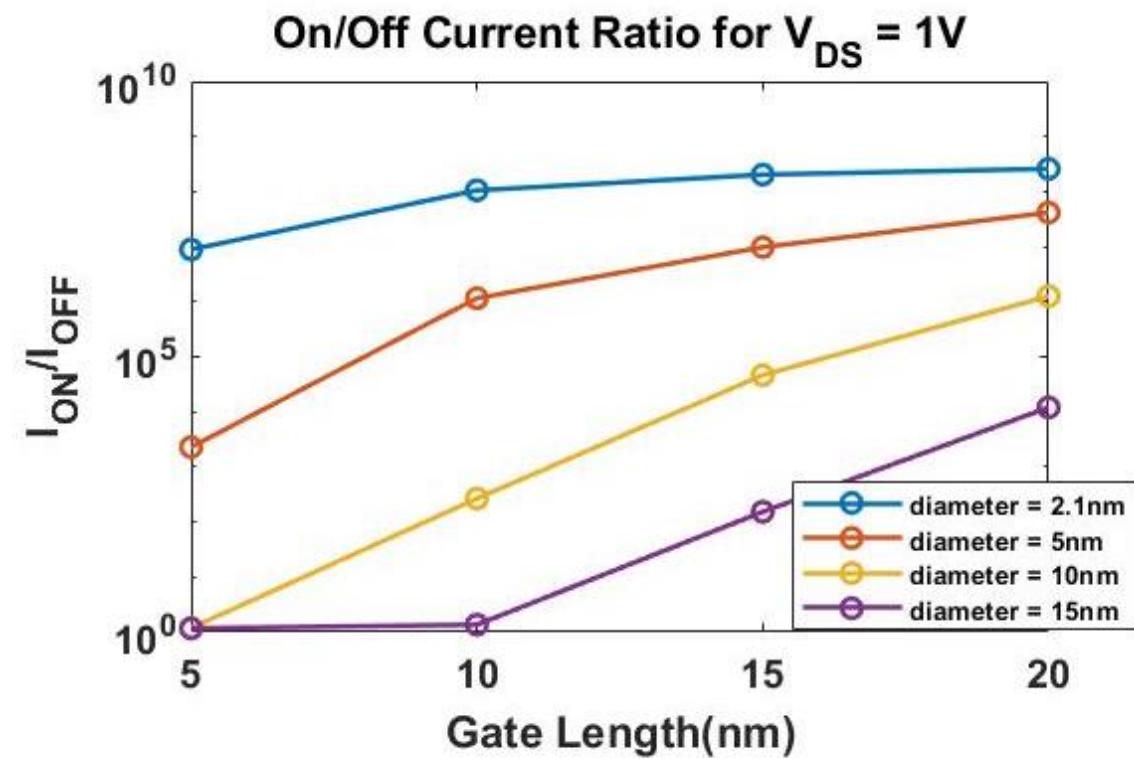

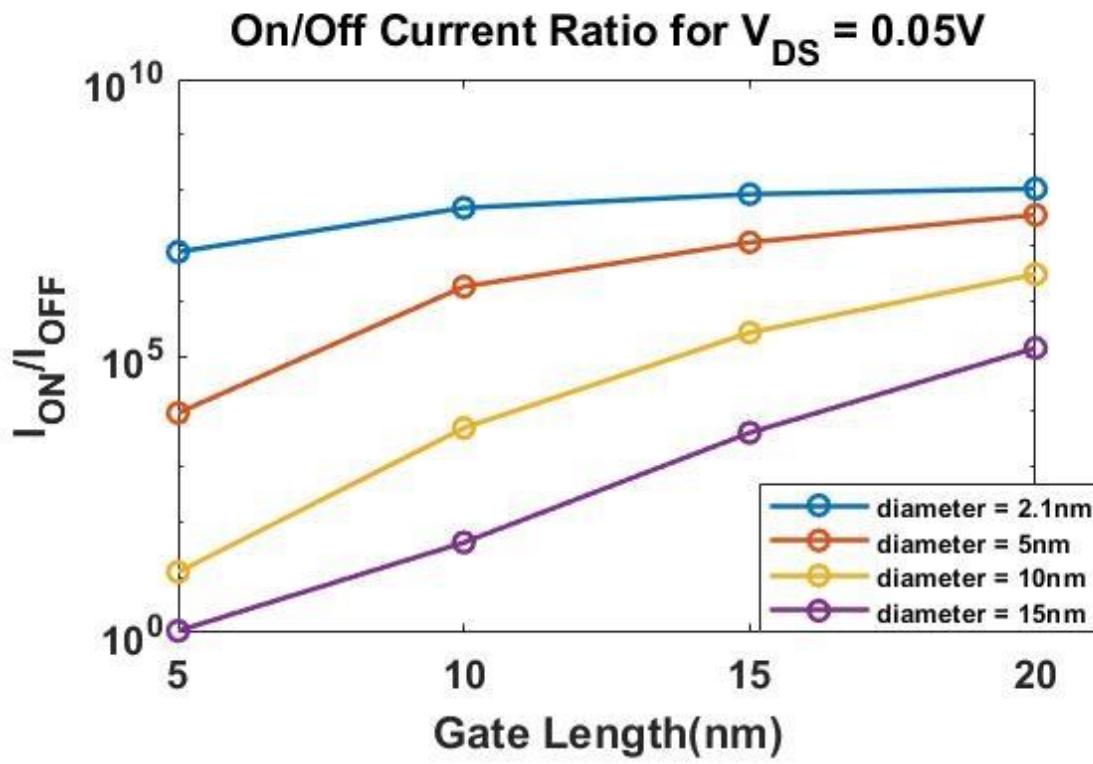

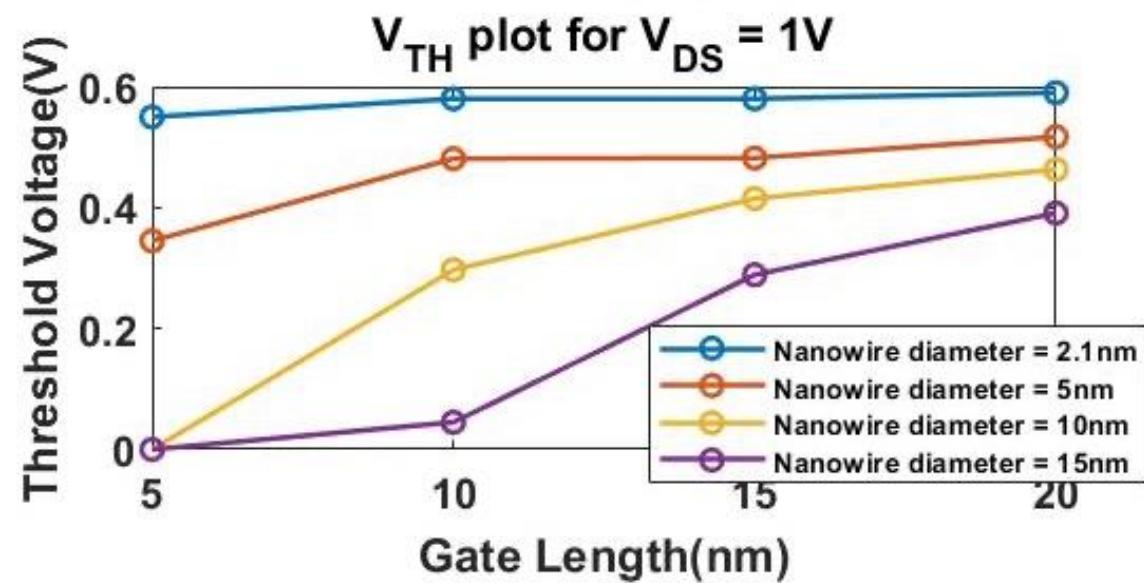

- The On/Off current ratio and subthreshold swing improves with decreasing diameter and increasing gate length (figure).

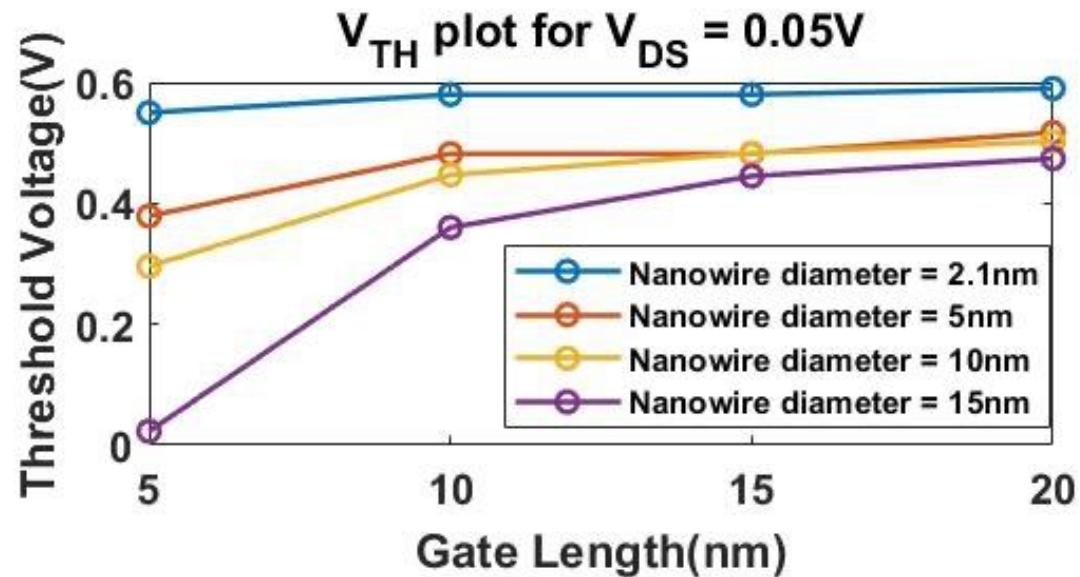

- The threshold voltage increases with increasing gate length and diameter (Appendix - [Nanowires with Drift Diffusion: Threshold Voltages](#)).

# Nanowire with Drift Diffusion (Quad Chart 2 of 2)

## Objective:

- Understand how energy band diagrams vary based on the scaling of the gate length and nanowire diameter.

## Problem:

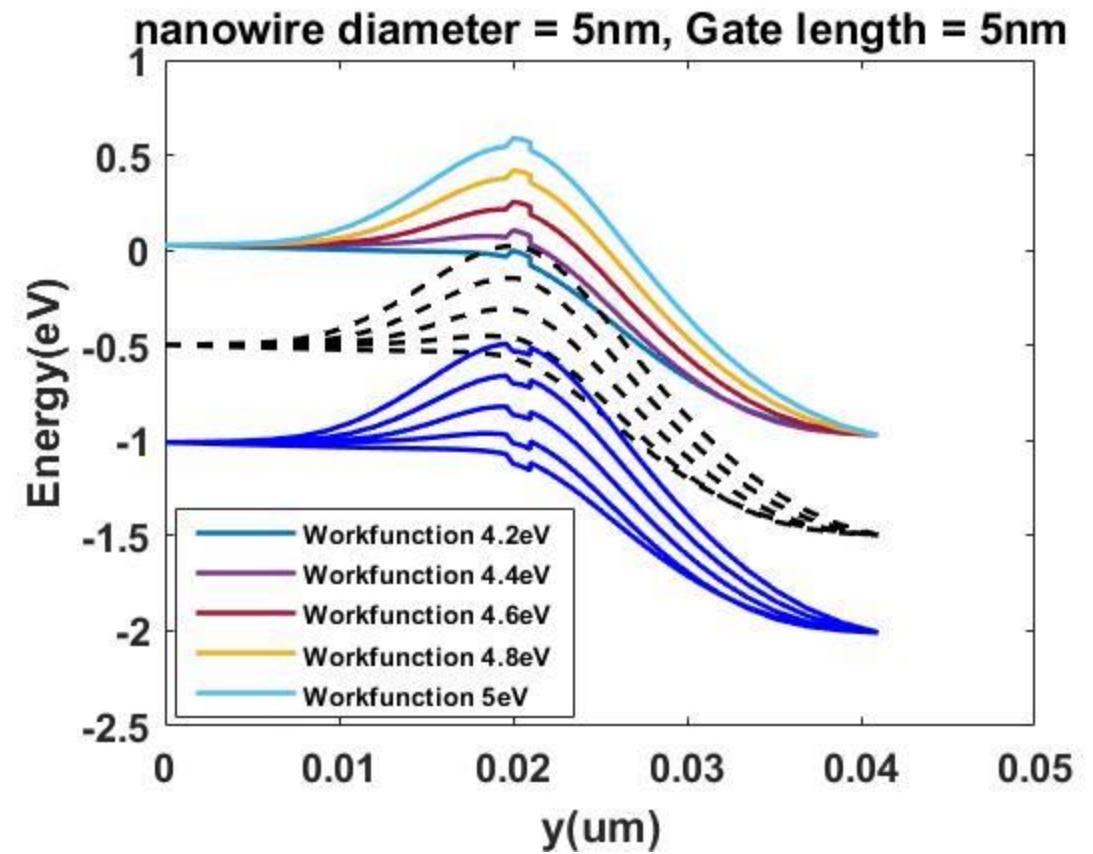

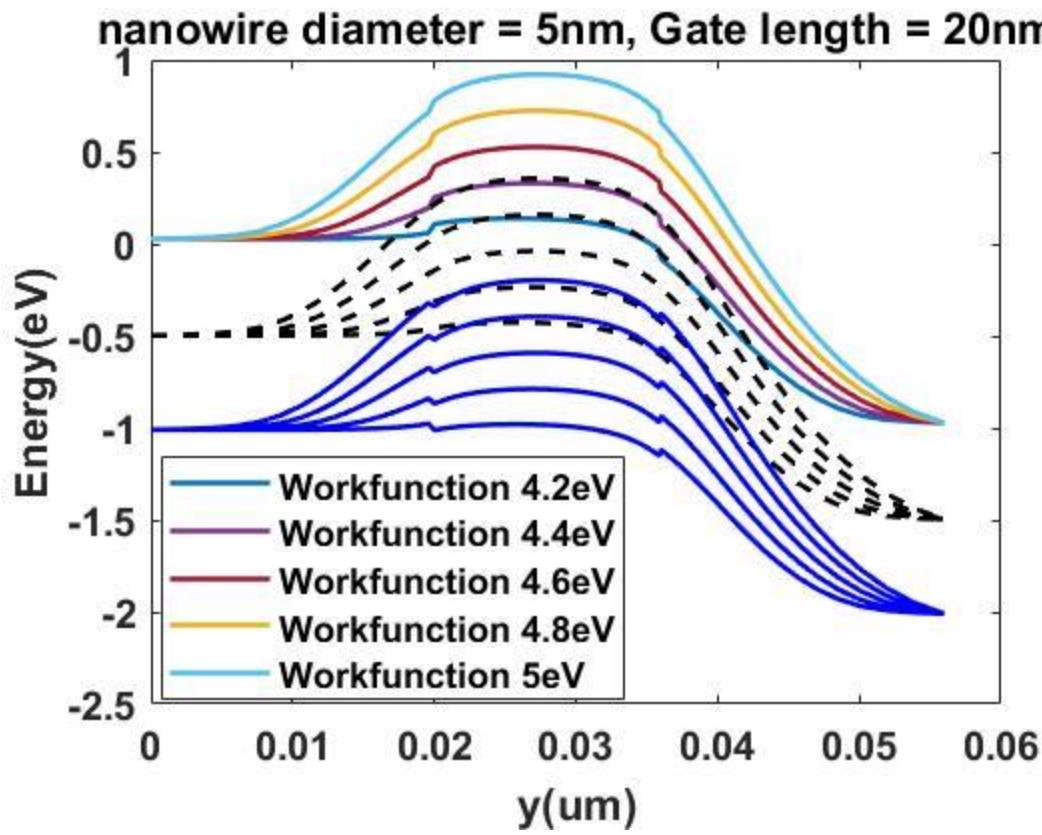

- How does the gate barrier height change as the gate length decreases?

## Approach:

- NanoHub's NANOFINFET tool was used to simulate device performance while varying the nanowire diameter and gate length.

- Please see [NANOFINFET Inputs](#) (located in the Appendix) for the inputs used in this simulation.

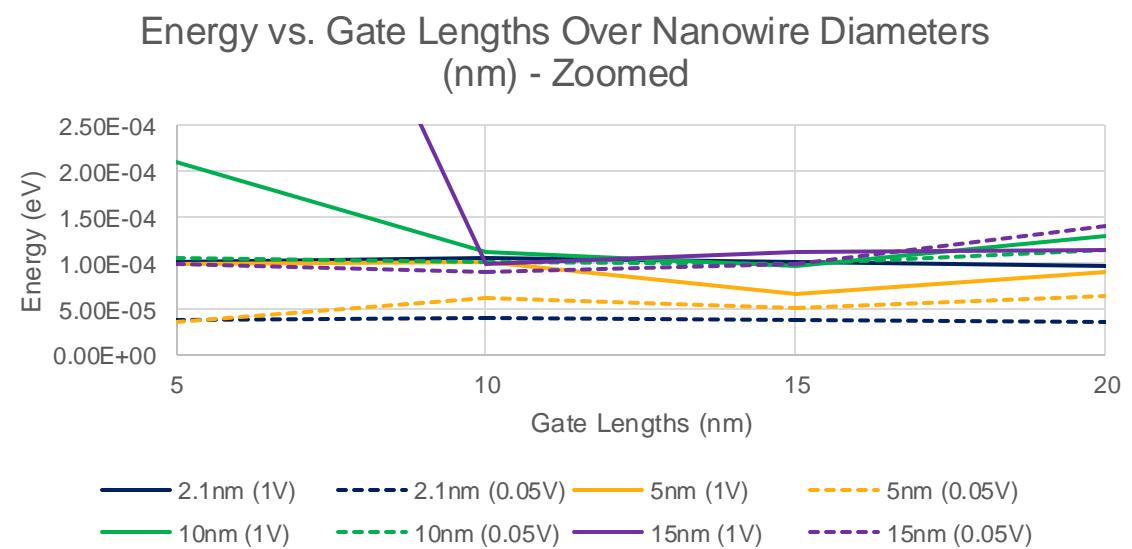

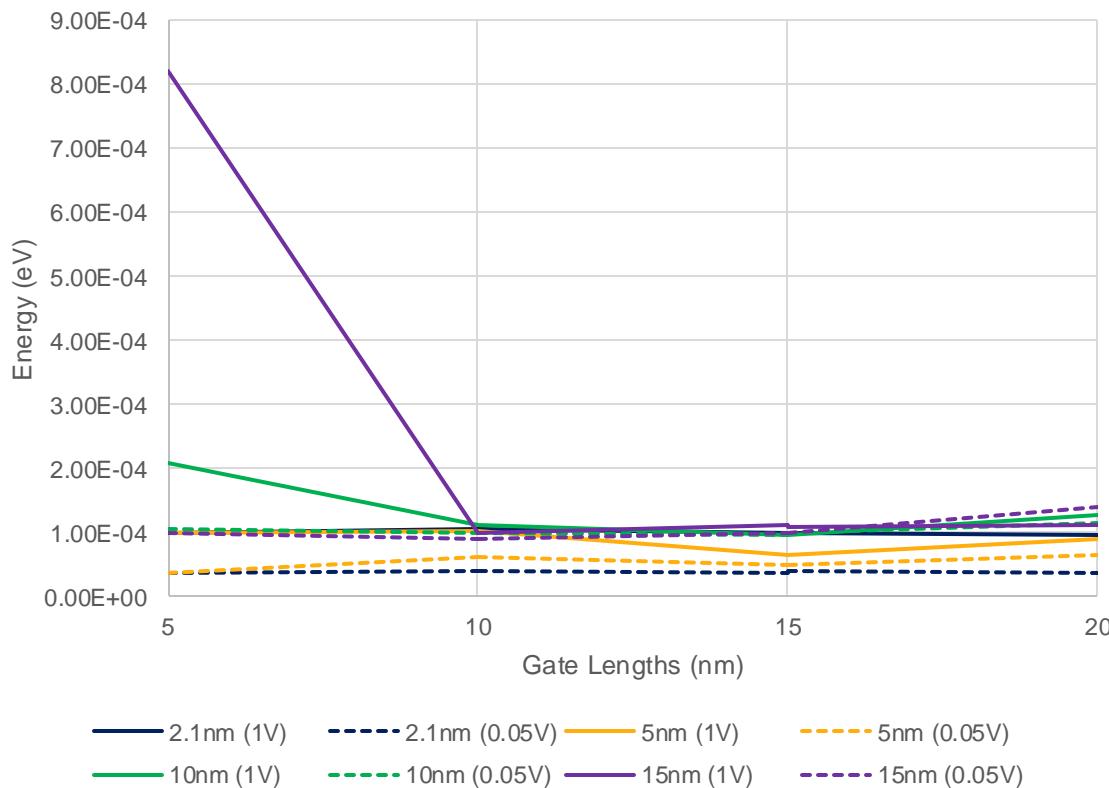

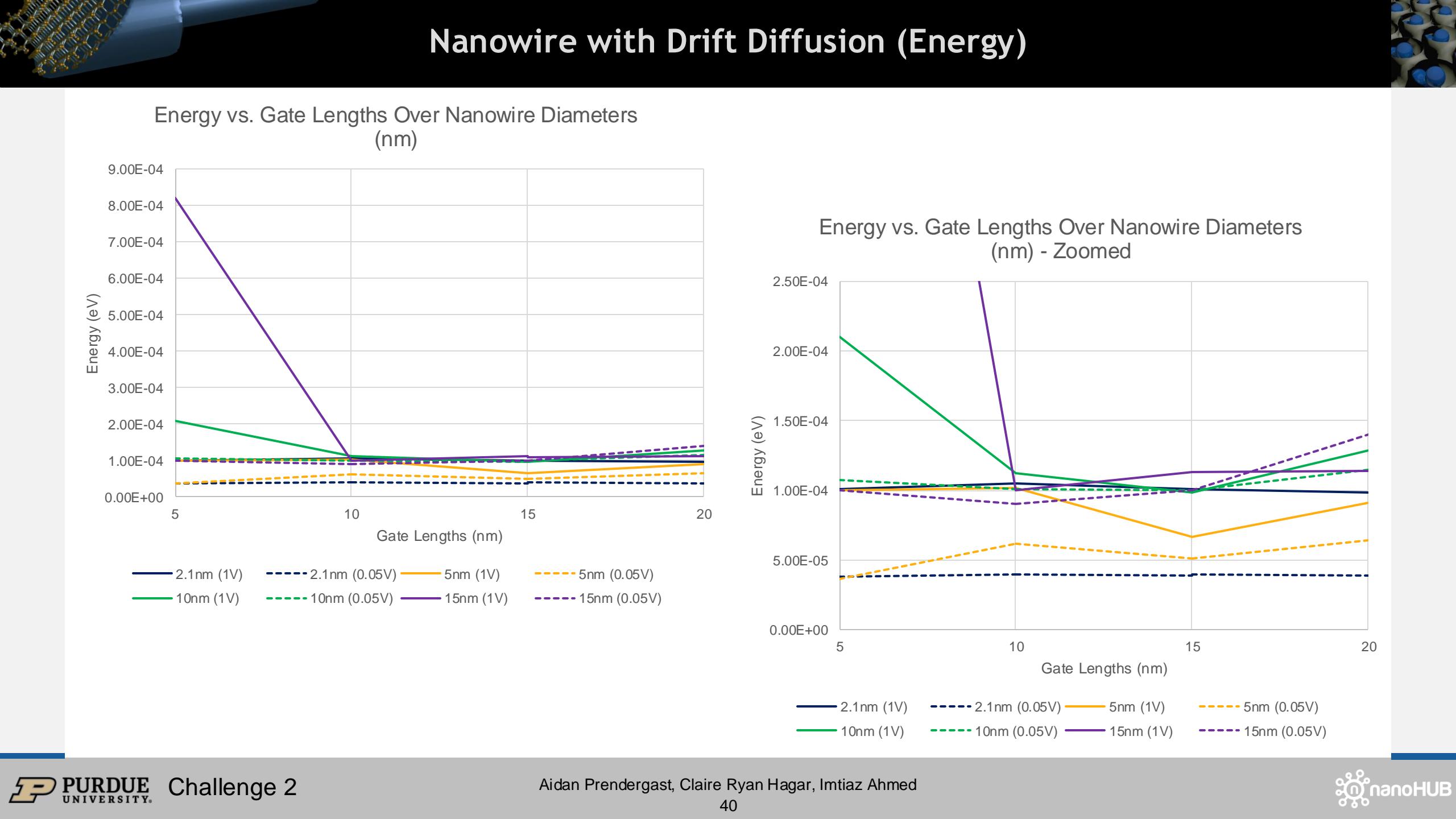

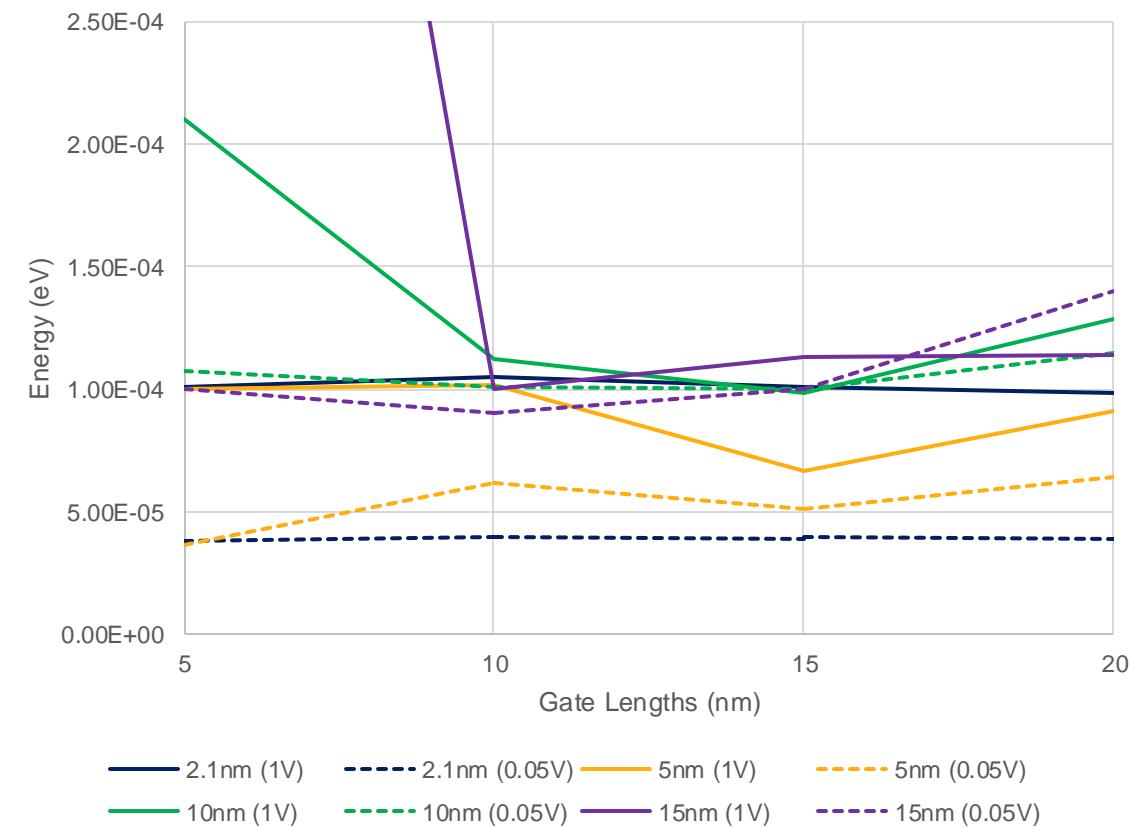

## Results / Impact:

- Please see [Energy vs. Gate Lengths](#) (located in the Appendix) for more detailed plots.

- Generally, the gate barrier height will increase as the gate length increases. Additionally, a decrease in source-drain voltage will result in a decrease of energy.

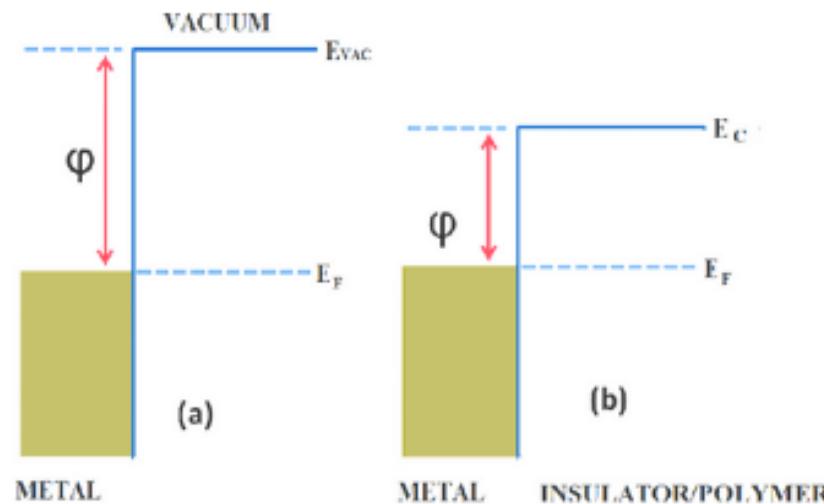

**Objective:**

- Understand workfunctions

**Problem:**

- What is the physics of "workfunction"?

- What are reasonable experimental values of workfunction?

**Results / Impact:**

- Workfunction is the minimum energy required to move an electron to a place away from the surface, but still close enough to be impacted by the surface's electric field. (see [1])

- For silicon, reasonable workfunction values range from 4.60 – 4.85 eV. (see [1])

**Approach:**

- The term workfunction was researched online to gain an understanding of its physics.

[1]

# Nanowire with Drift Diffusion - Workfunction Variations and Gate Potential Analysis (Quad Chart 2 of 2)

## Objective:

- Understand how a long vs short gate length nanowire effects the I-V characteristics.

## Problem:

- The ON/OFF current ratio, threshold voltage, and subthreshold swing can all be impacted by changing parameters.

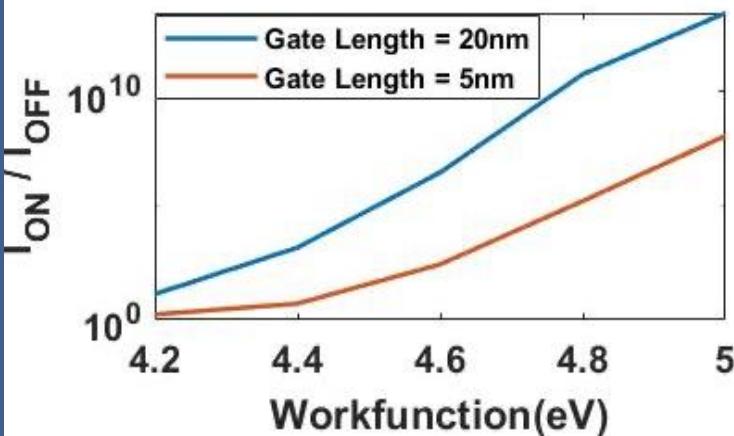

## Results / Impact:

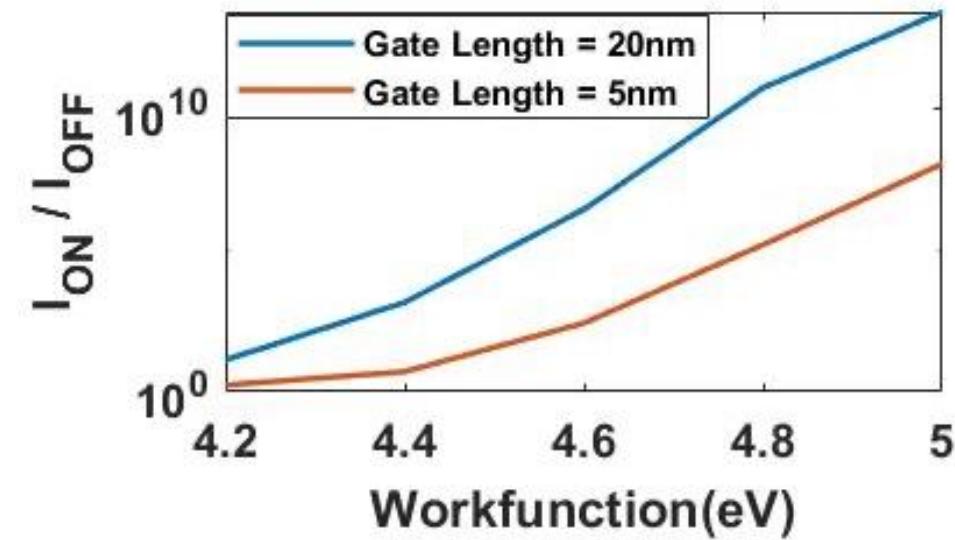

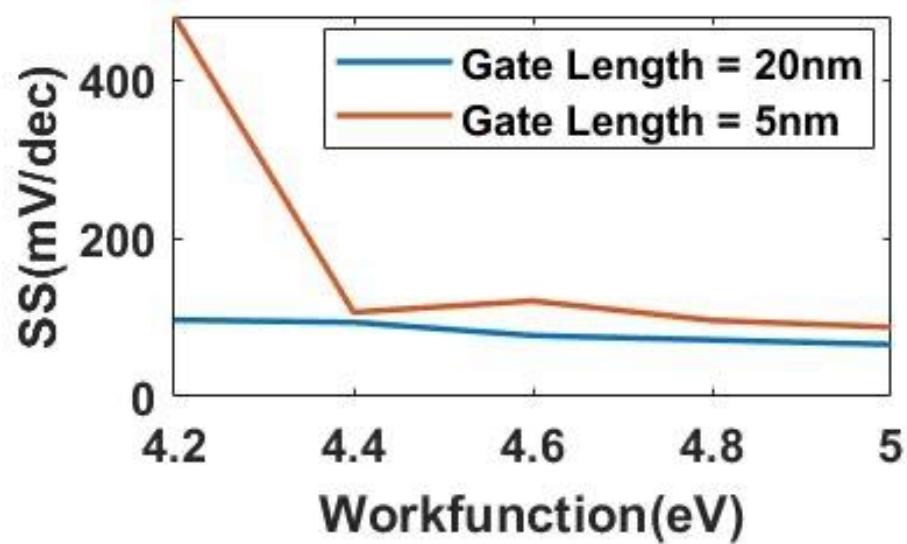

- As workfunction increases, the on/off current ratio increases (figure), and subthreshold swing decreases (appendix) as a result.

- Normalization of I-V data by choosing a workfunction is often done for getting rid of device-to-device variation when performing comparison

- Please see [Transistor Parameters](#) in the Appendix for additional plots.

## Approach:

- NanoHub's NANOFINFET tool was used to simulate device performance while varying the gate contact workfunction.

- Please see [NANOFINFET Inputs](#) (located in the Appendix) for the inputs used in this simulation.

Smaller Gate device with low workfunction

→ barrier too low

→ higher I<sub>OFF</sub>

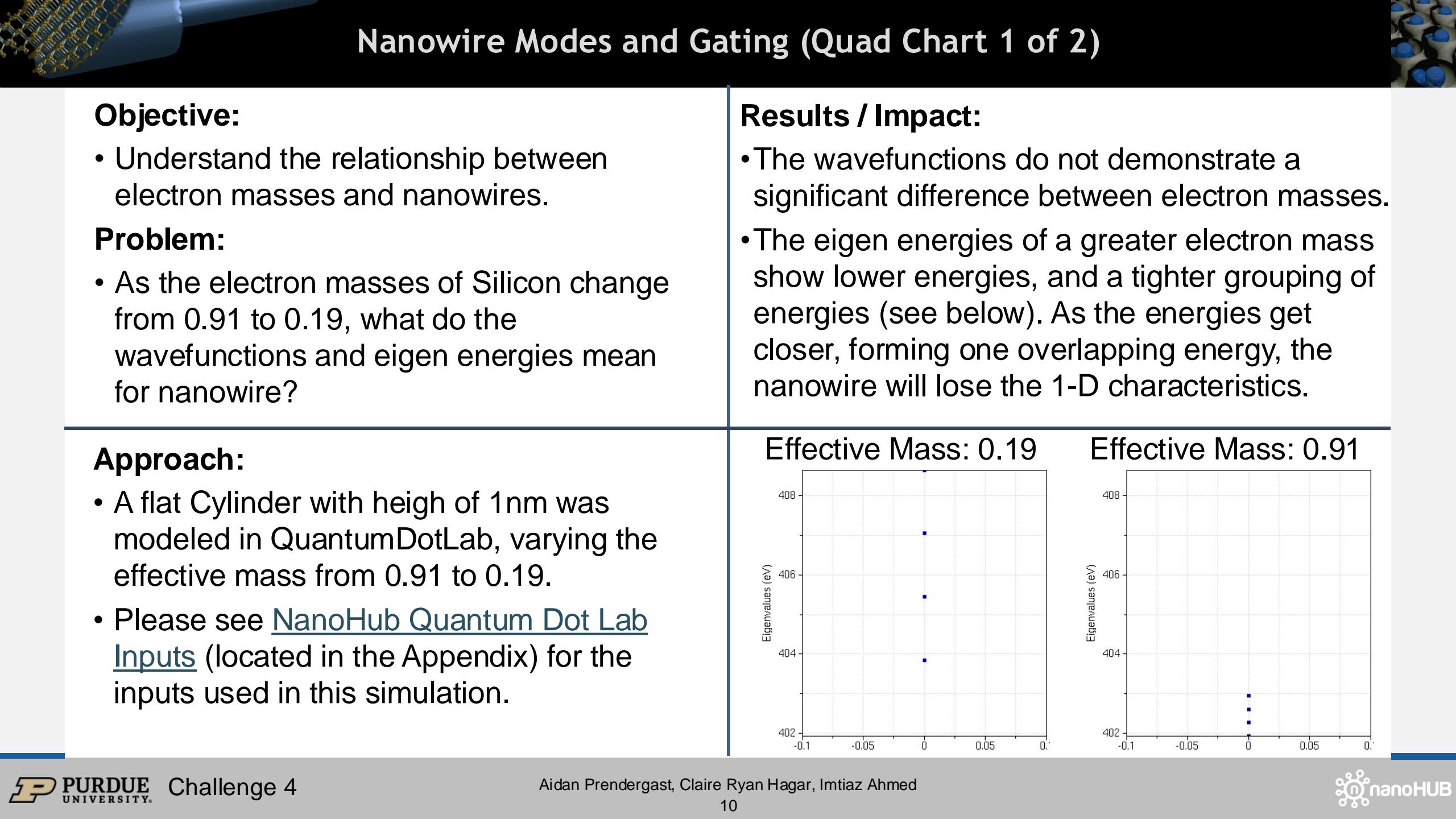

# Nanowire Modes and Gating (Quad Chart 1 of 2)

## Objective:

- Understand the relationship between electron masses and nanowires.

## Problem:

- As the electron masses of Silicon change from 0.91 to 0.19, what do the wavefunctions and eigen energies mean for nanowire?

## Approach:

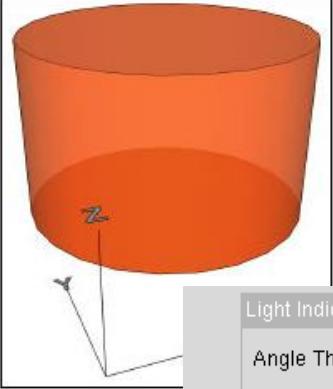

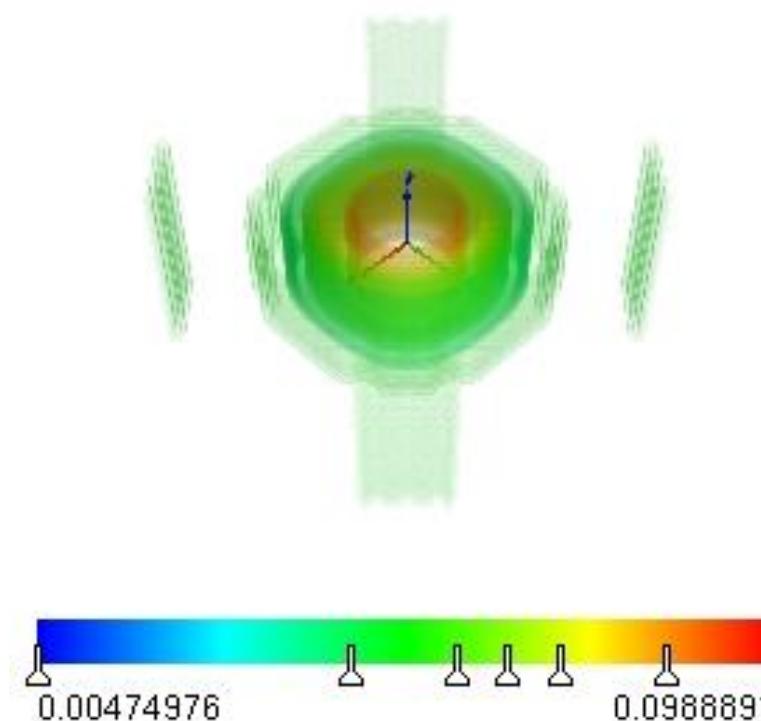

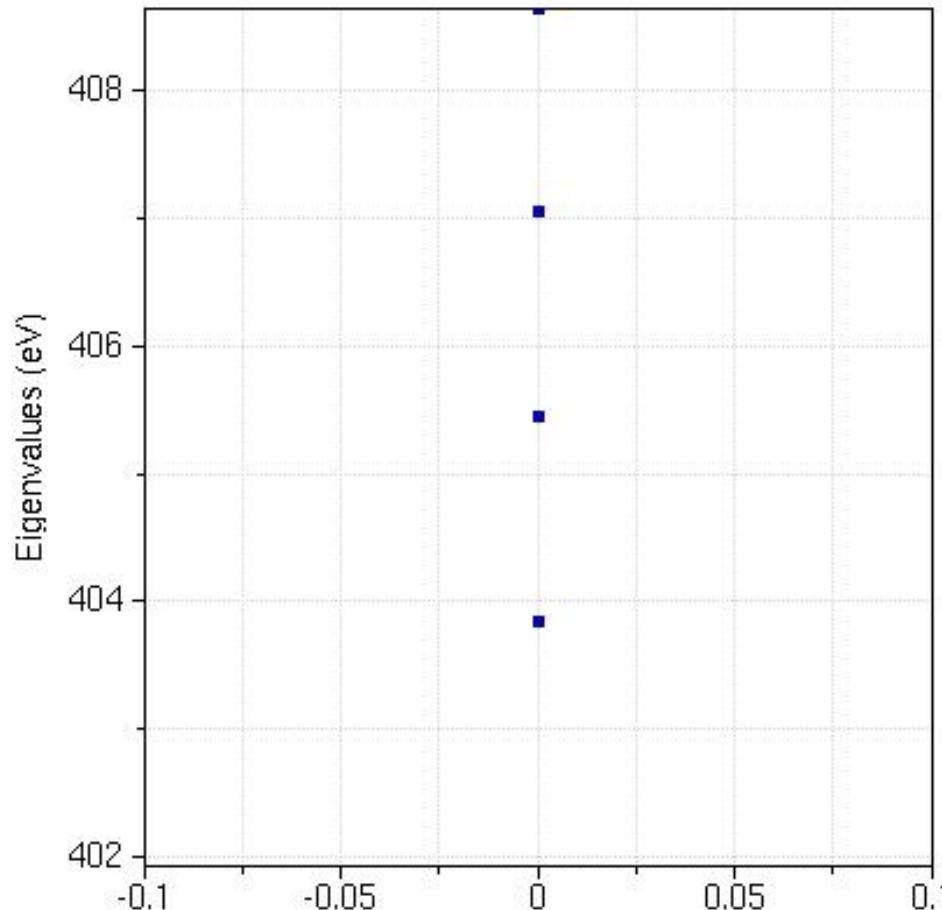

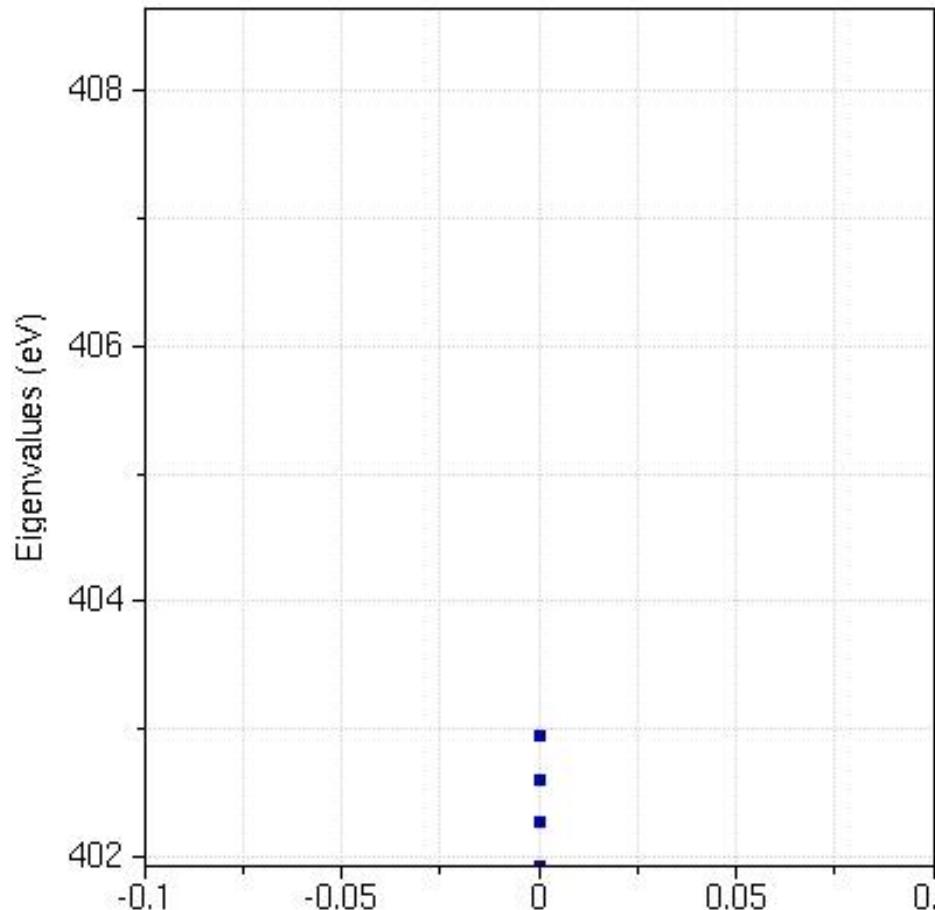

- A flat Cylinder with height of 1nm was modeled in QuantumDotLab, varying the effective mass from 0.91 to 0.19.

- Please see [NanoHub Quantum Dot Lab Inputs](#) (located in the Appendix) for the inputs used in this simulation.

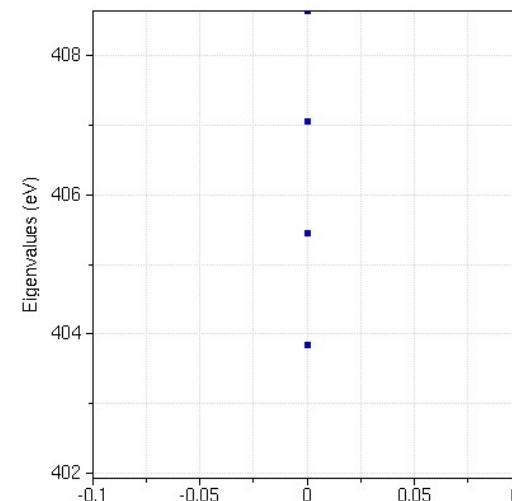

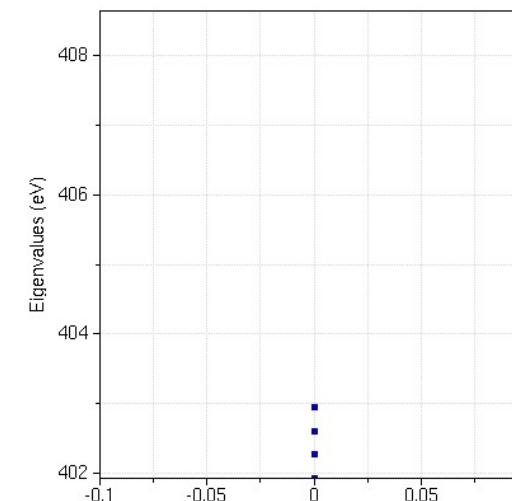

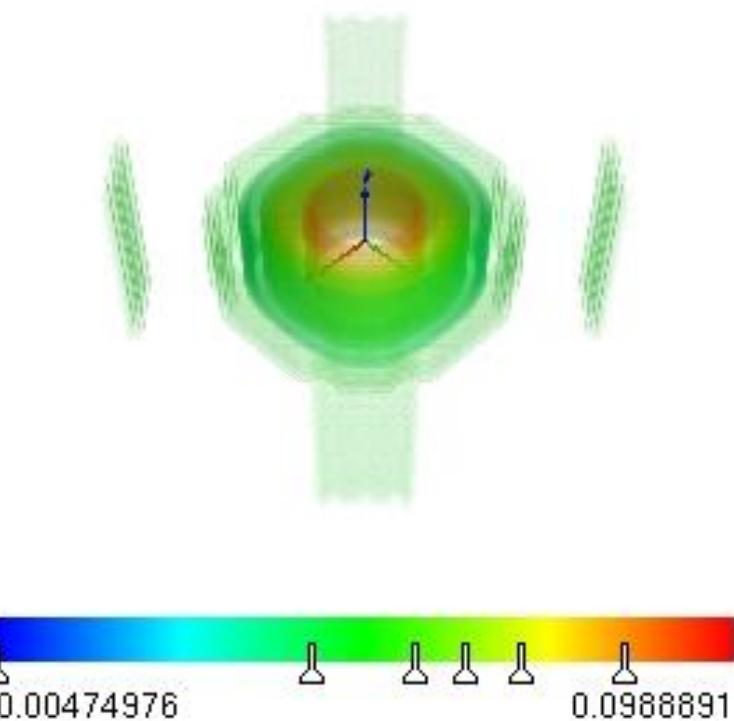

## Results / Impact:

- The wavefunctions do not demonstrate a significant difference between electron masses.

- The eigen energies of a greater electron mass show lower energies, and a tighter grouping of energies (see below). As the energies get closer, forming one overlapping energy, the nanowire will lose the 1-D characteristics.

Effective Mass: 0.19

Effective Mass: 0.91

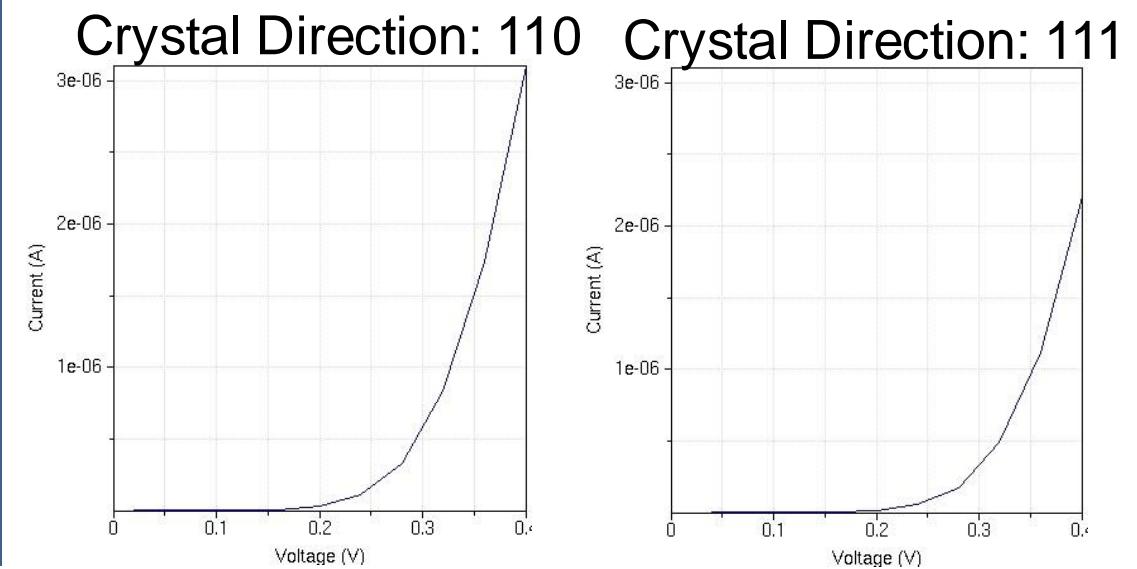

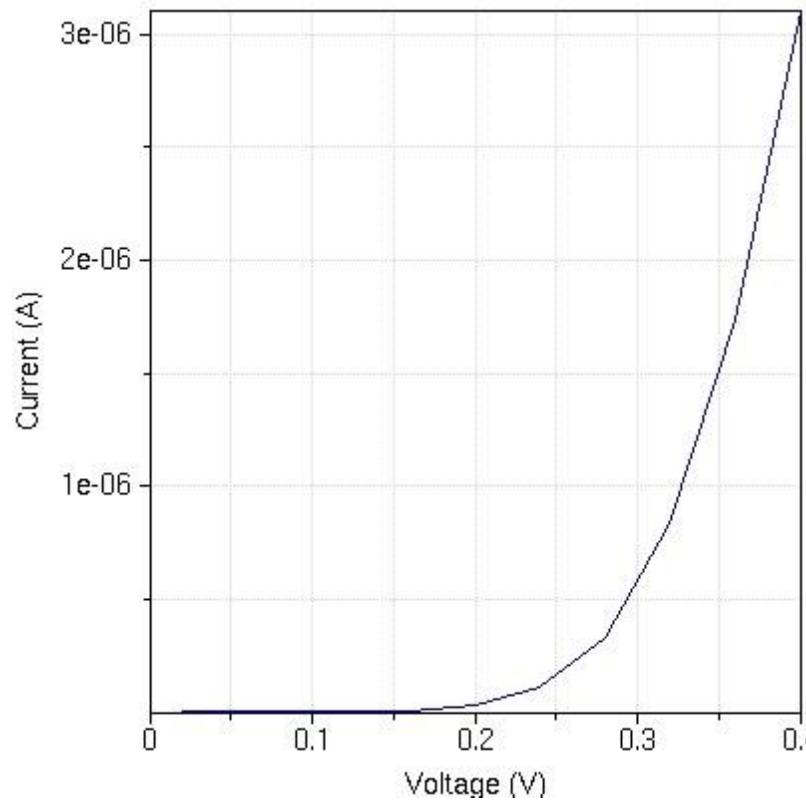

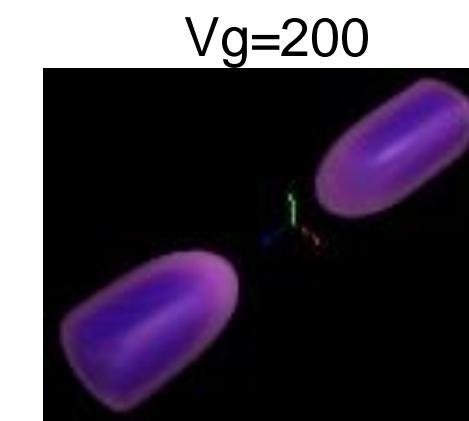

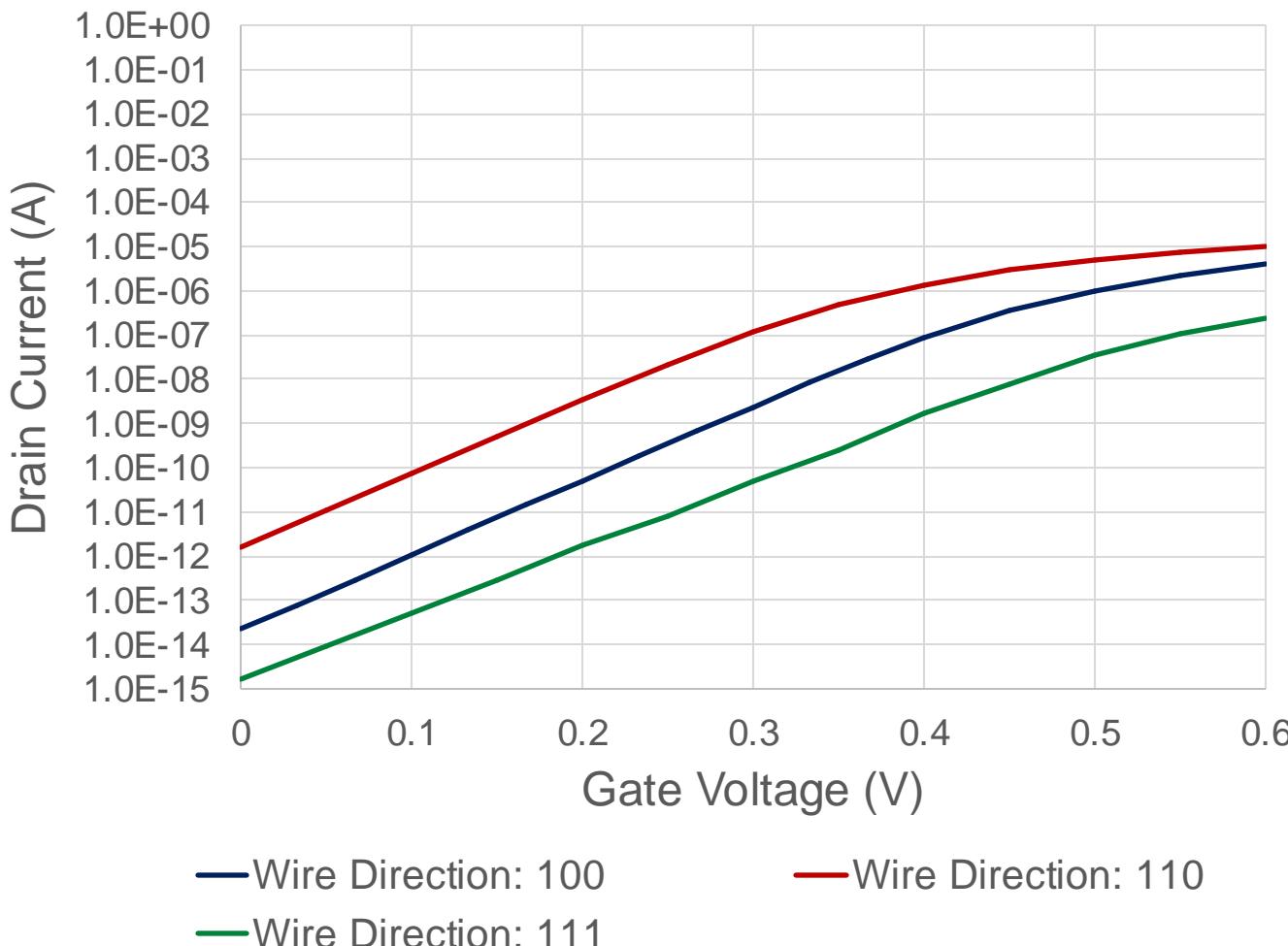

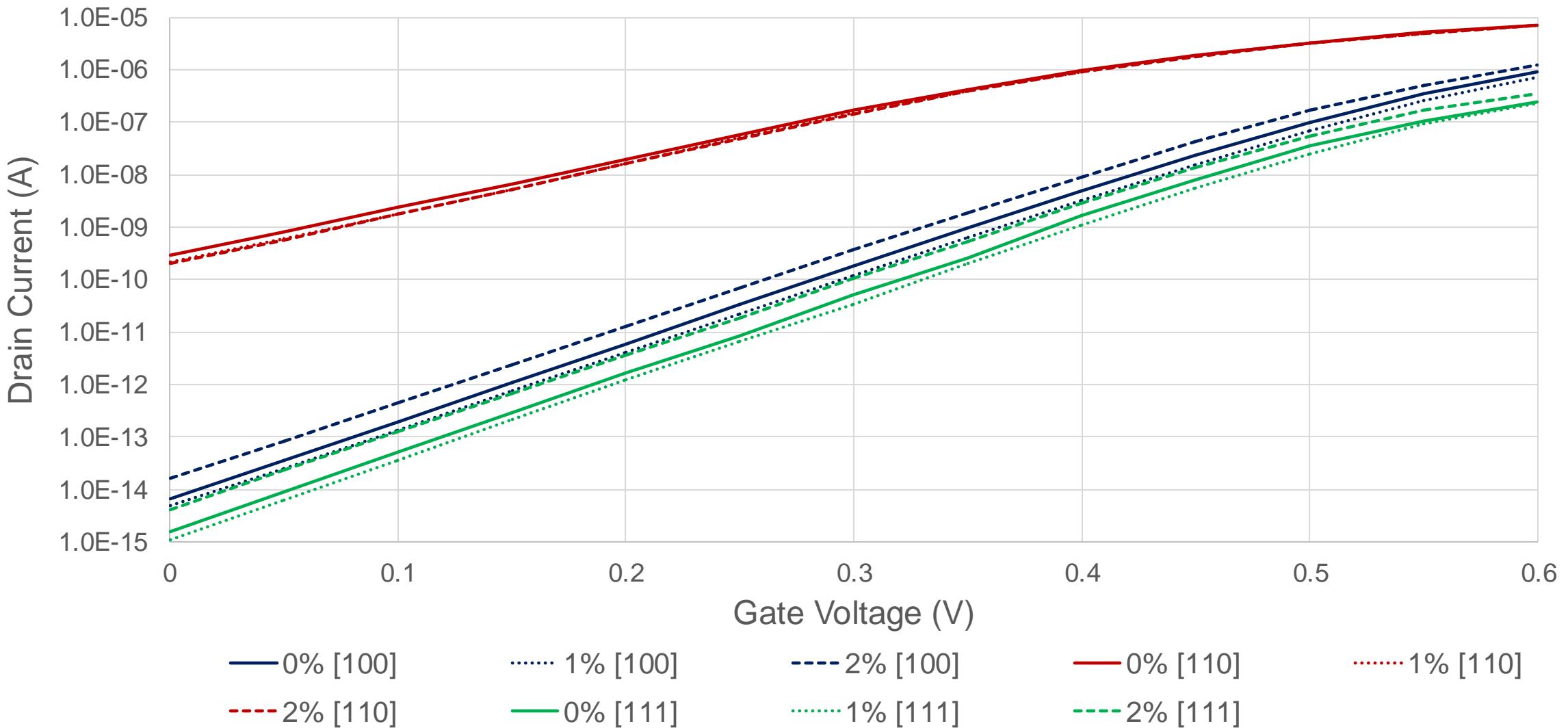

# Nanowire Modes and Gating (Quad Chart 2 of 2)

## Objective:

- Compare the I-Vg curves between difference crystal directions of Silicon.

## Problem:

- What is the difference in I-Vg curves between 100, 110, and 111 crystal directions?

## Approach:

- A silicon nanowire of diameter 2nm was modeled in Nanowire, varying the crystal direction.

- Please see [NanoHub Nanowire Inputs](#) (located in the Appendix) for the inputs used in this simulation.

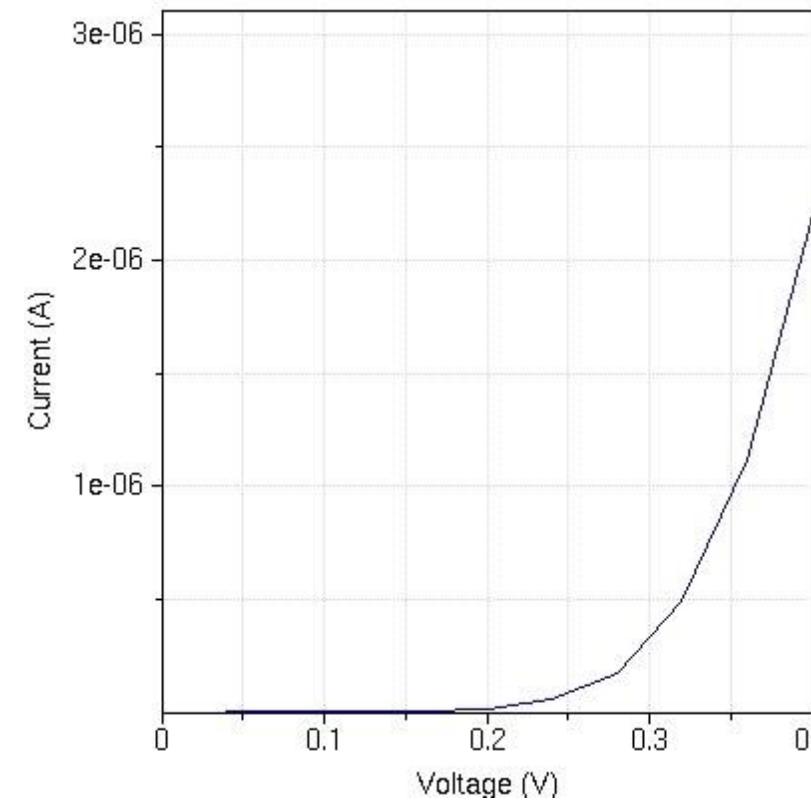

## Results / Impact:

- Shown below is the comparison of 110 and 111 crystal directions. The I-Vg curve of 100 does not exist.

- Shown in [1D Electron Densities](#) and [3D Electron Densities](#) (located in the Appendix) are the comparisons of the electron densities. They are very similar between crystal directions.

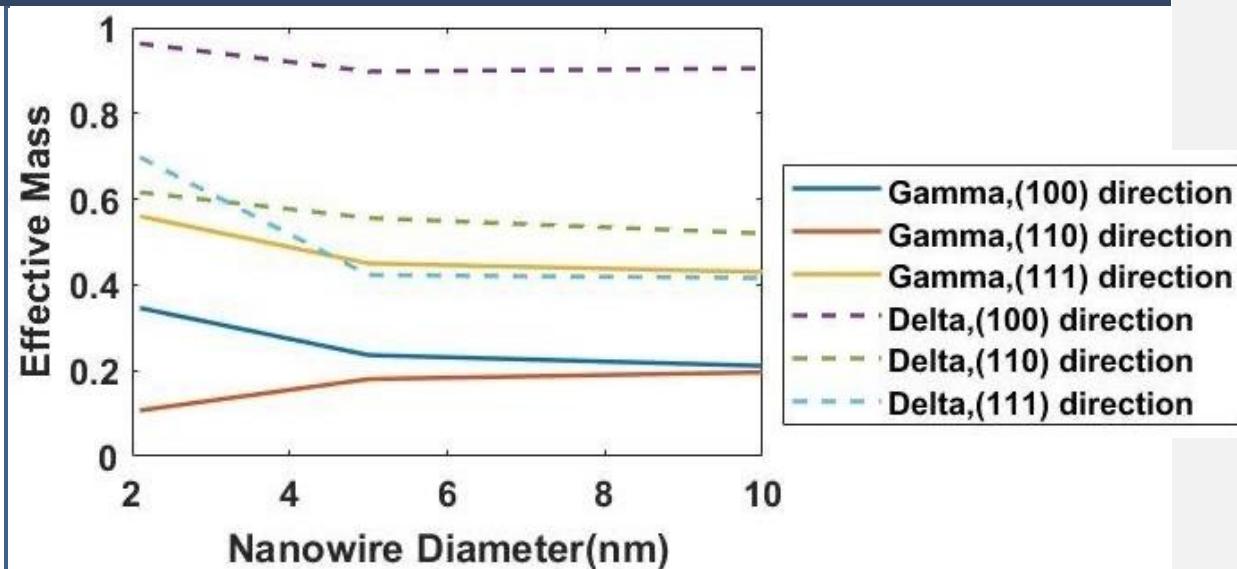

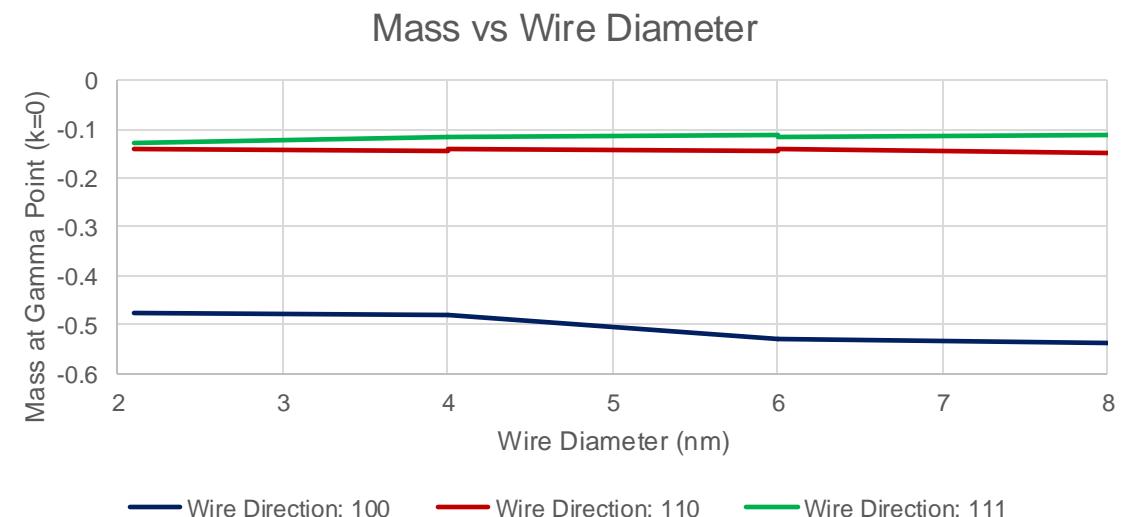

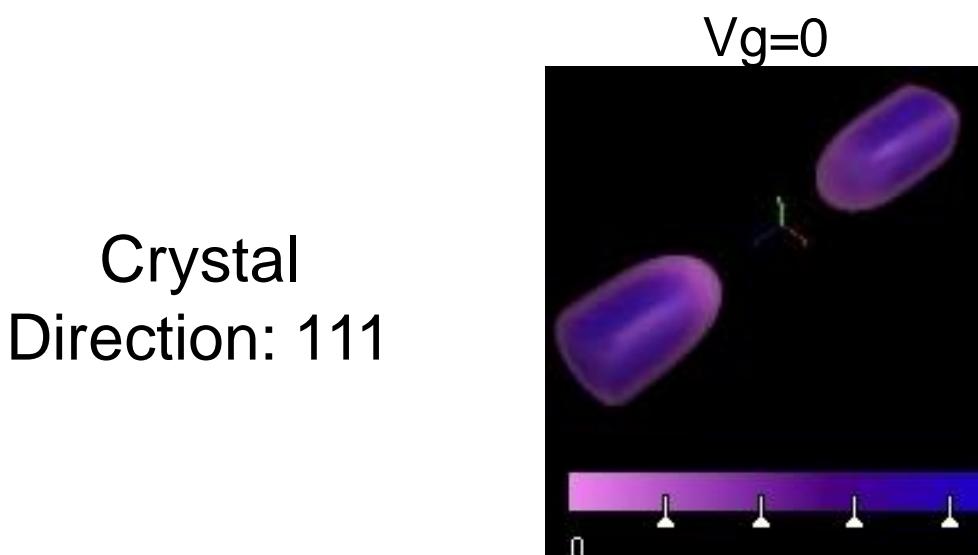

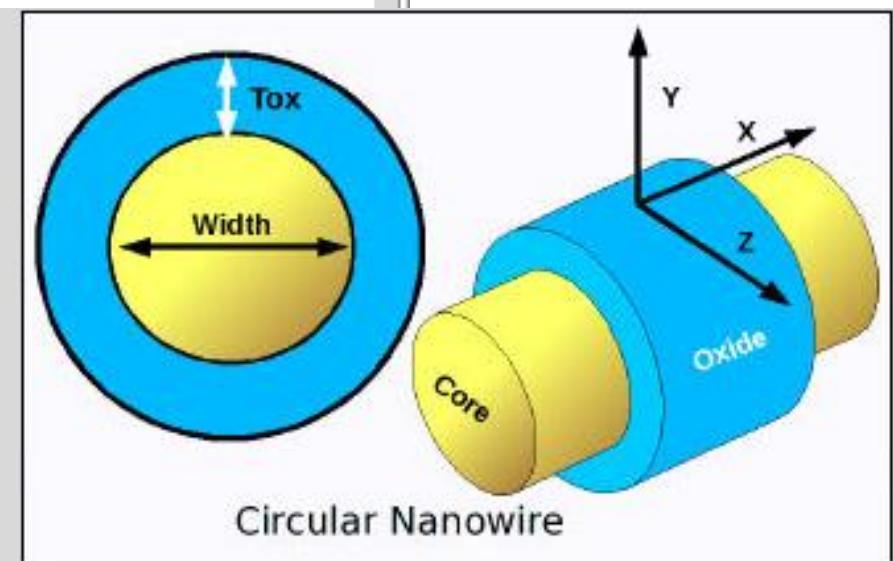

# Nanowire Realistic Bandstructure (Quad Chart 1 of 2)

## Objective:

- Understand the bandstructure of a nanowire.

## Problem:

- How does the mass at the different points in a nanowire vary with diameter and transport directions?

## Approach:

- A silicon nanowire was modeled in NanoHub's BandstructureLab, varying the nanowire transport direction and diameter.

- Please see [NanoHub BandstructureLab Inputs](#) (located in the Appendix) for the inputs used in this simulation.

## Results / Impact:

- The mass is greater at the Delta line (when  $k>0$ ) than at the Gamma point (when  $k=0$ ).

- Generally, the mass will decrease as the nanowire diameter increases.

- Please see [Nanowire Realistic Bandstructure \(Masses\)](#) (in the Appendix) for more detailed plots.

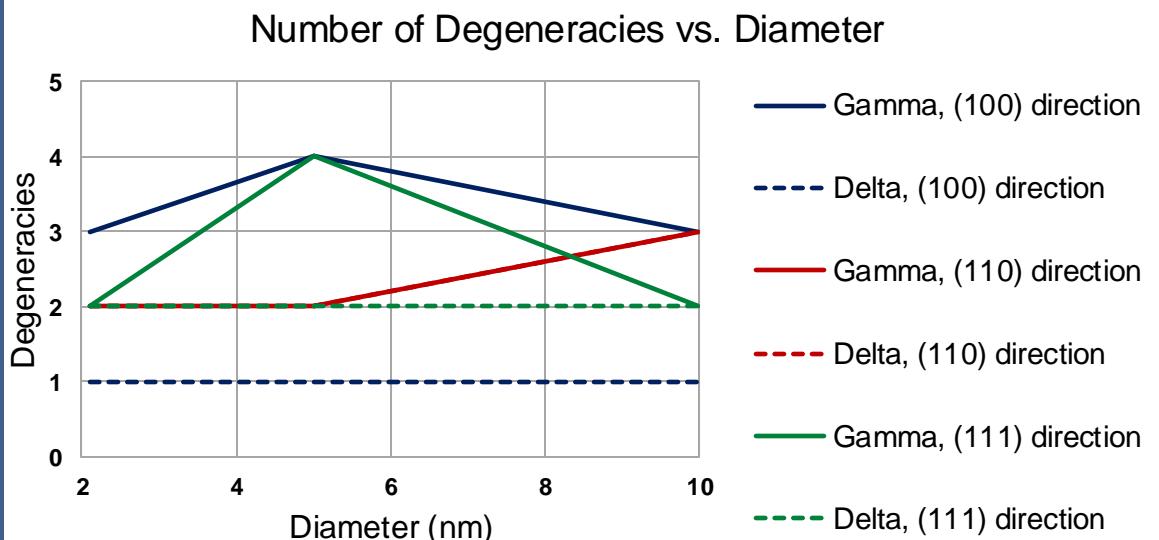

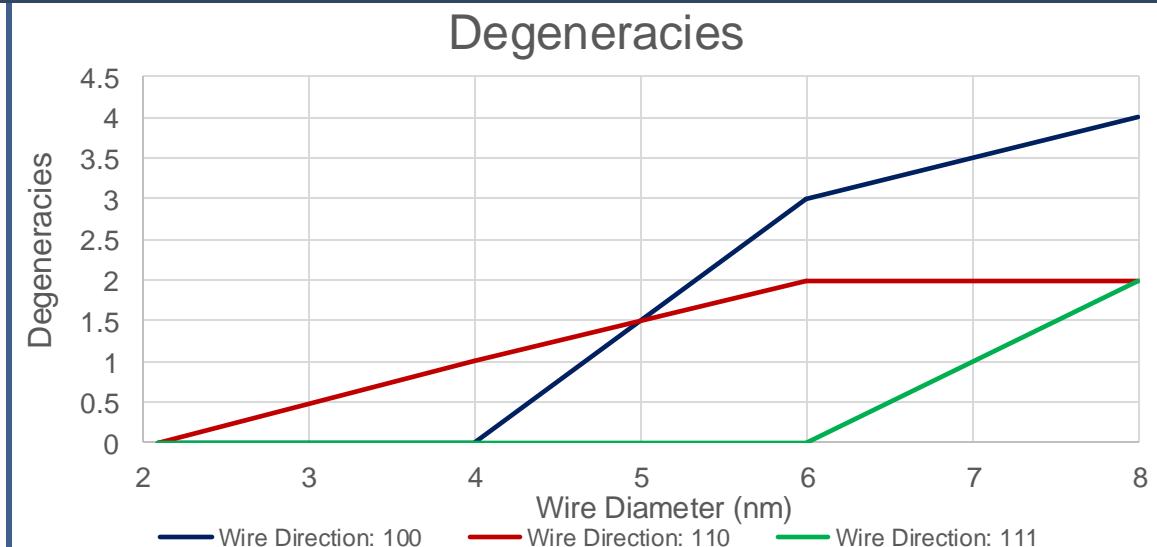

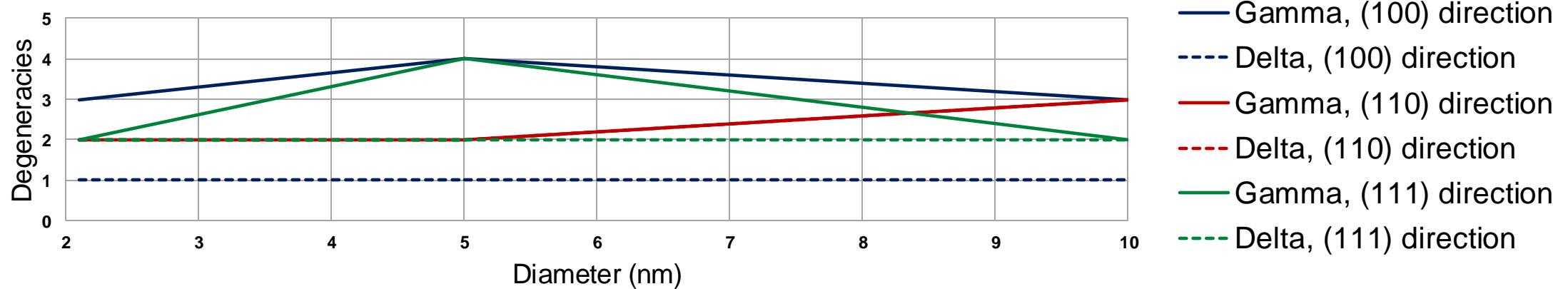

# Nanowire Realistic Bandstructure (Quad Chart 2 of 2)

## Objective:

- Understand the bandstructure of a nanowire.

## Problem:

- How does the degeneracies at the different points in a nanowire vary with diameter and transport directions?

## Results / Impact:

- For 100 and 111 transport directions, there are more degeneracies at the Gamma point.

- The number of degeneracies vary in no significant pattern based on nanowire diameter.

- Please see [Nanowire Realistic Bandstructure \(Degeneracies\)](#) (in the Appendix) for more detailed plots and detailed data Table

## Approach:

- A silicon nanowire was modeled in NanoHub's BandstructureLab, varying the nanowire transport direction and diameter.

- Please see [NanoHub BandstructureLab Inputs](#) (located in the Appendix) for the inputs used in this simulation.

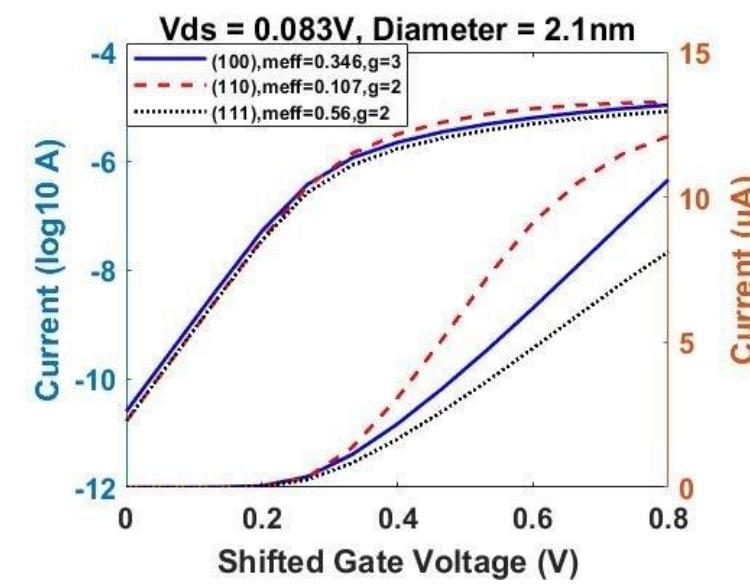

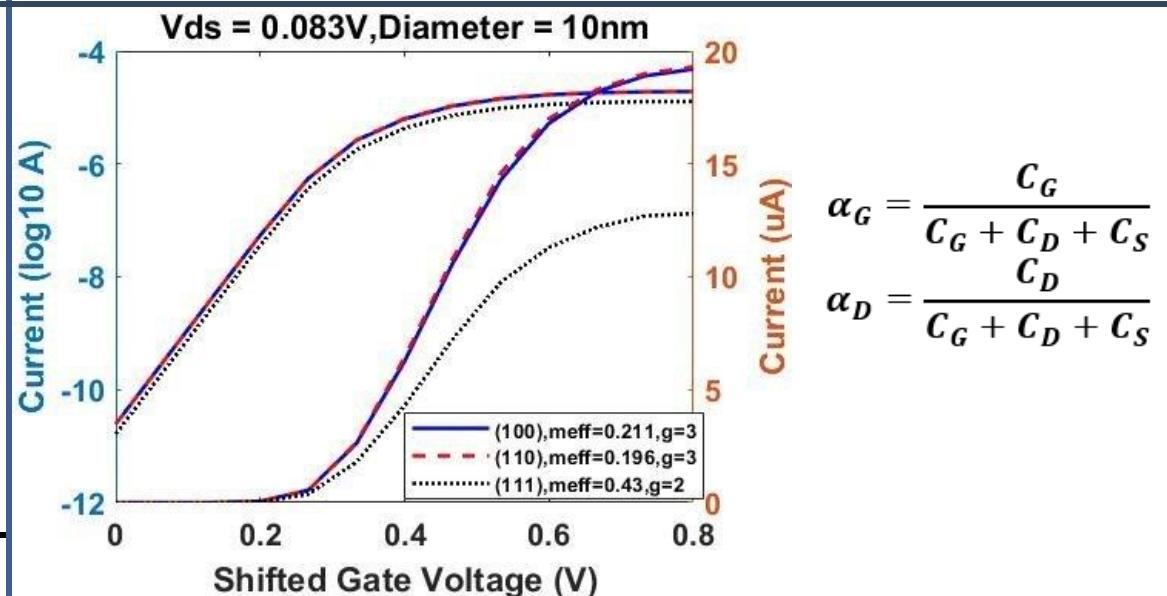

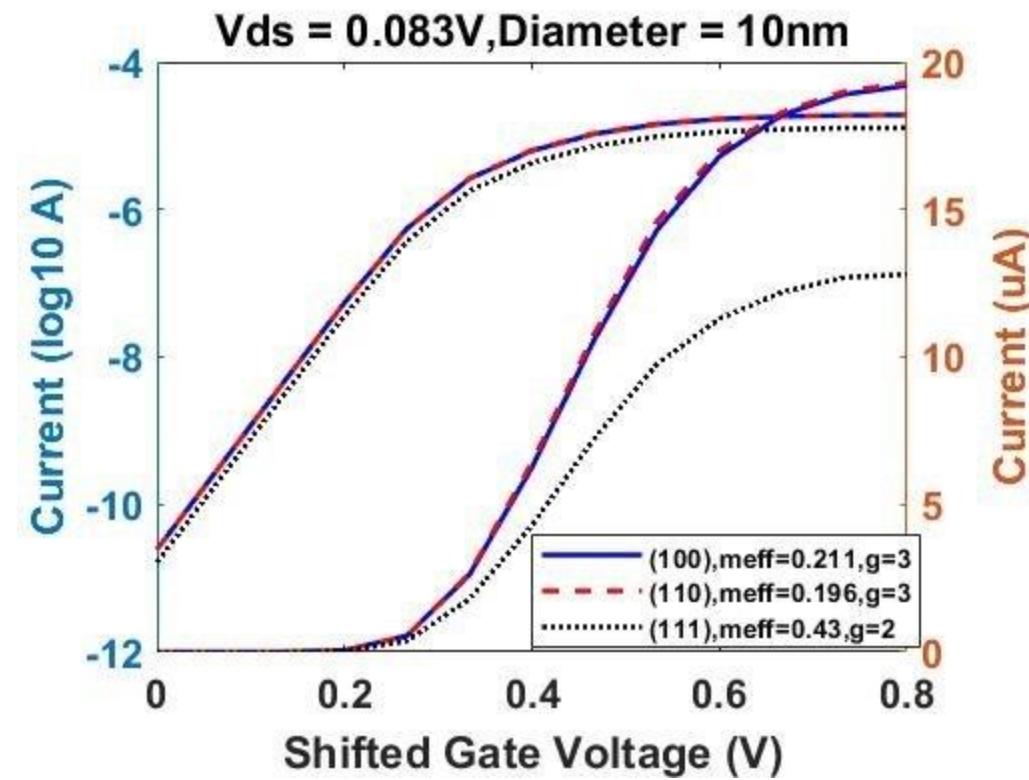

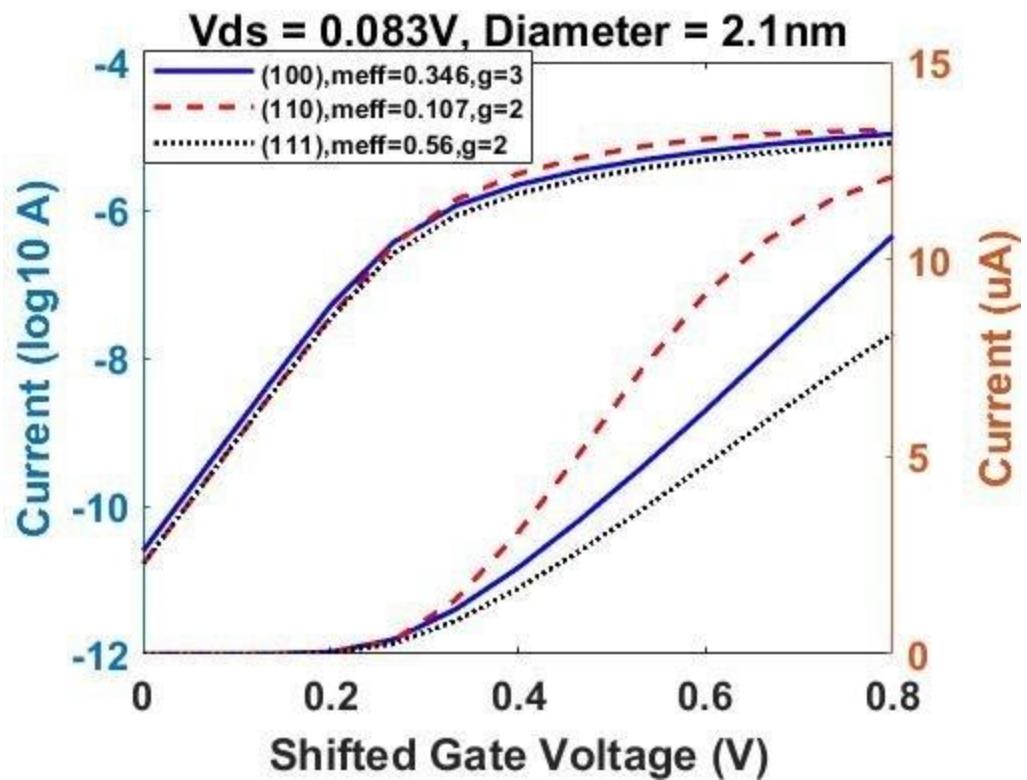

# Nanowire Top-of-Barrier Transport (Quad Chart 1 of 2)

## Objective:

- Understand electron transport through nanowires.

## Problem:

- How does the I-V curve differ between nanowire transport directions (100, 110, and 111) and differing diameters (2.1nm and 10nm)?

## Approach:

- A silicon nanowire was modeled in NanoHub's FETtoy tool, varying the nanowire transport direction and diameter. The masses and degeneracies from Challenge #5 were also utilized (please see [inputs](#)).

- Please see [NanoHub FETtoy Inputs](#) (in the Appendix) for the inputs used in this simulation.

## Results / Impact:

- The currents are generally largest in the 110 direction and smallest in the 111 direction.

- The currents increase with an increase in nanowire diameter.

- Please see [Nanowire Top-of-Barrier Transport \(I-V Curves\)](#) for both plots.

# Nanowire Top-of-Barrier Transport (Quad Chart 2 of 2)

## Objective:

- Understand electron transport through nanowires.

## Problem:

- How do the inputs alphaG and alphaD relate realistic capacitances?

## Approach:

- A silicon nanowire was modeled in NanoHub's FETtoy tool, varying the nanowire transport direction and diameter. The masses and degeneracies from Challenge #5 were also utilized (please see [inputs](#)).

- Please see [NanoHub FETtoy Inputs](#) ( in the Appendix) for the inputs used in this simulation.

## Results / Impact:

- alphaG and alphaD quantities refer to Gate and Drain control parameter respectively.

- Ideally the Gate must have complete control over the channel and not drain. However, due to Drain Induced Barrier Lowering (DIBL), transistor sees a lowering of threshold voltage, mostly in short channel devices.

- Results in Drain control over Channel.

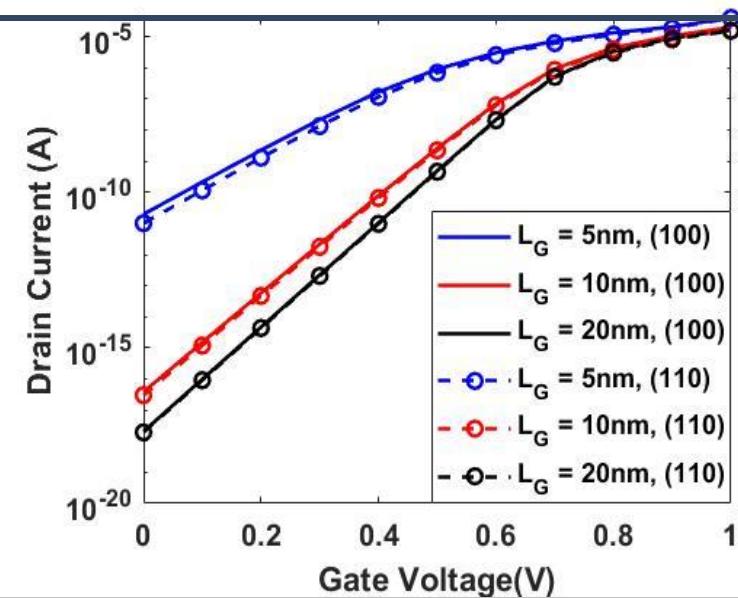

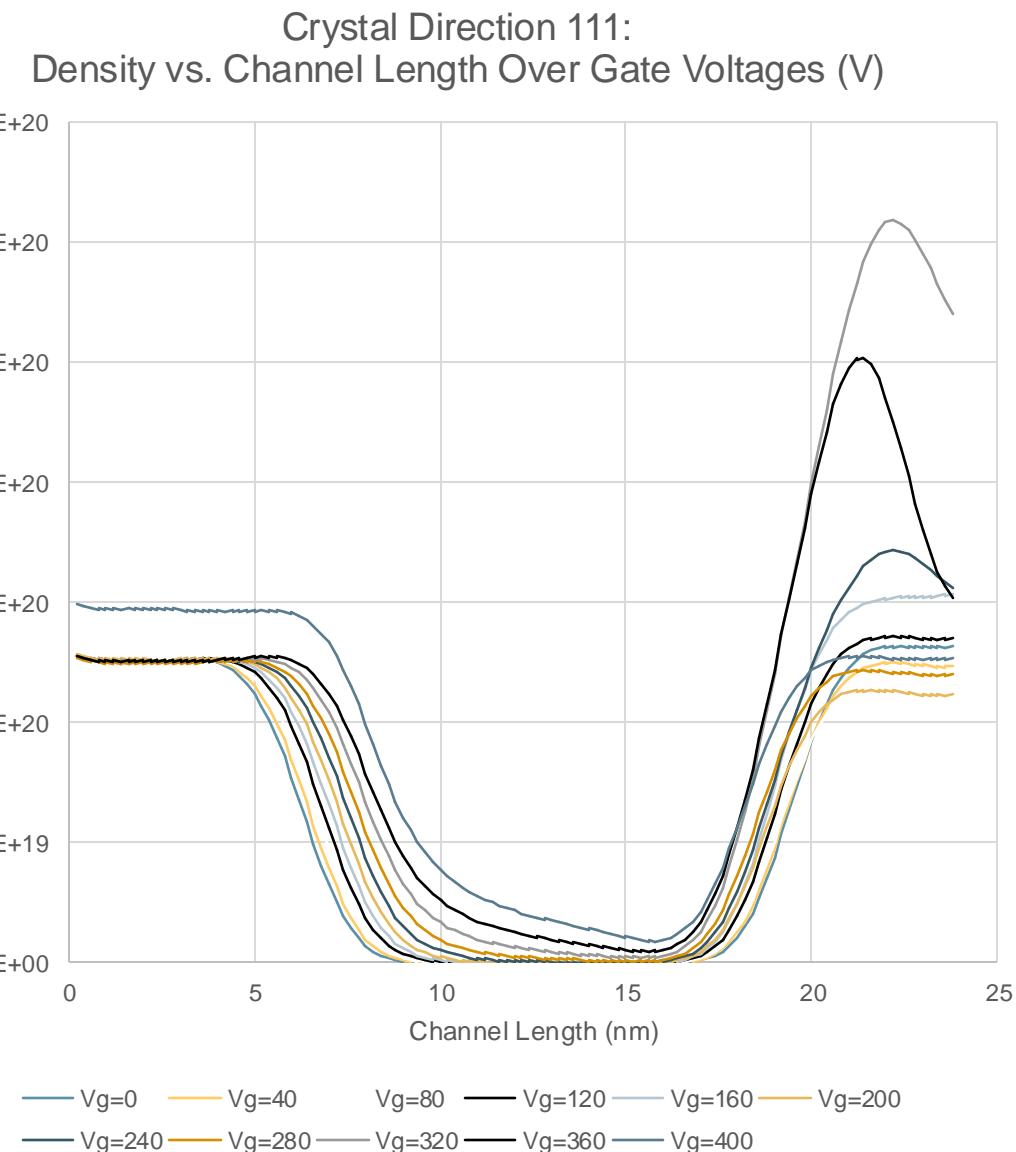

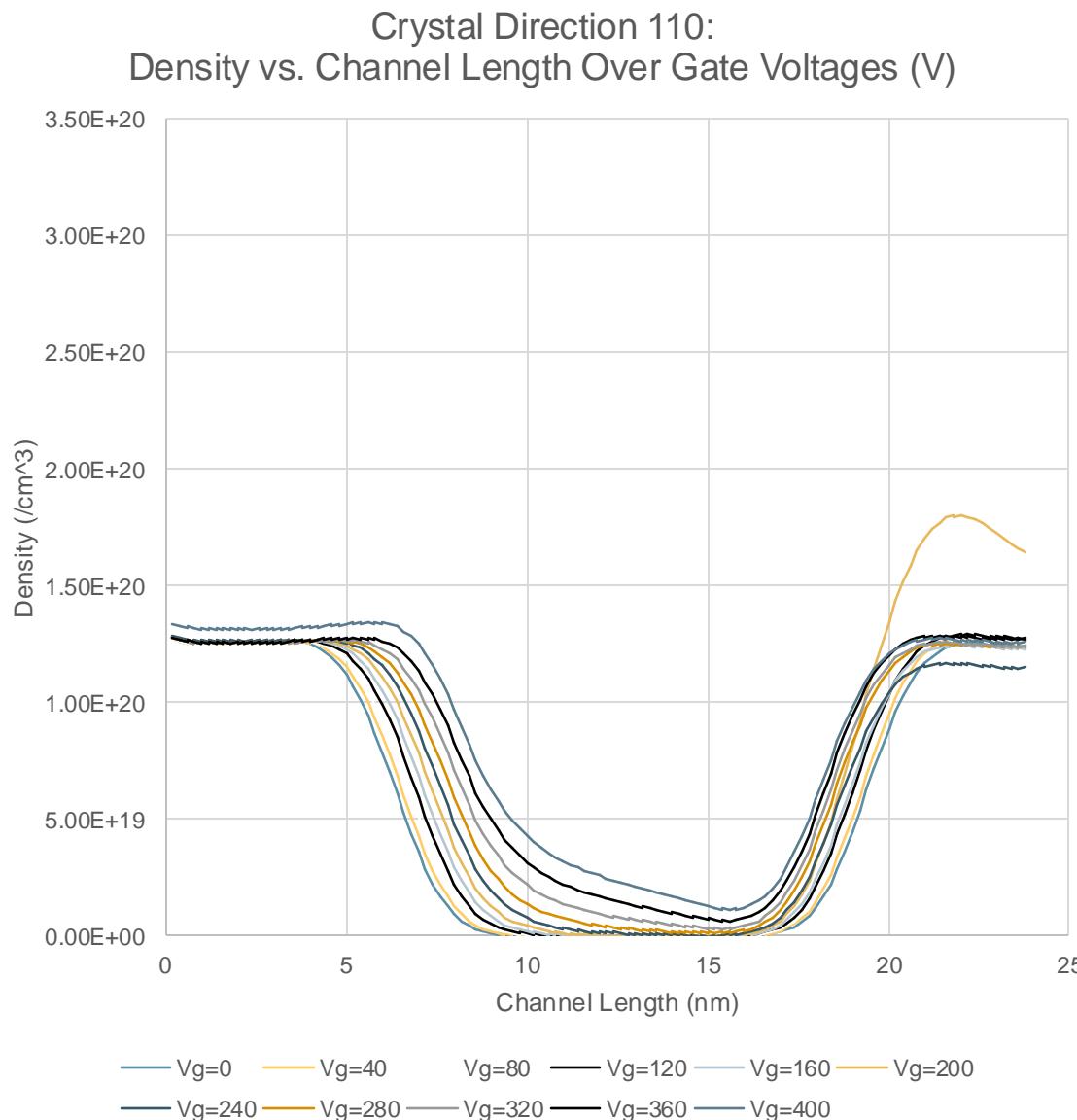

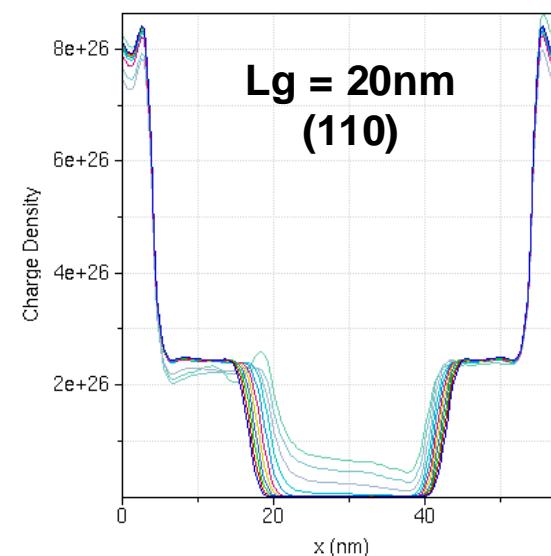

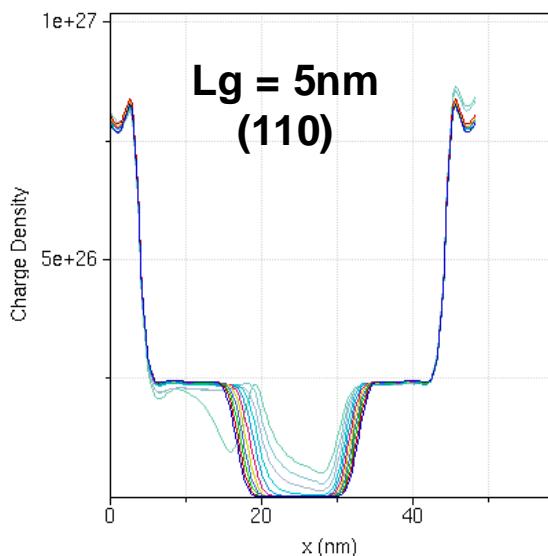

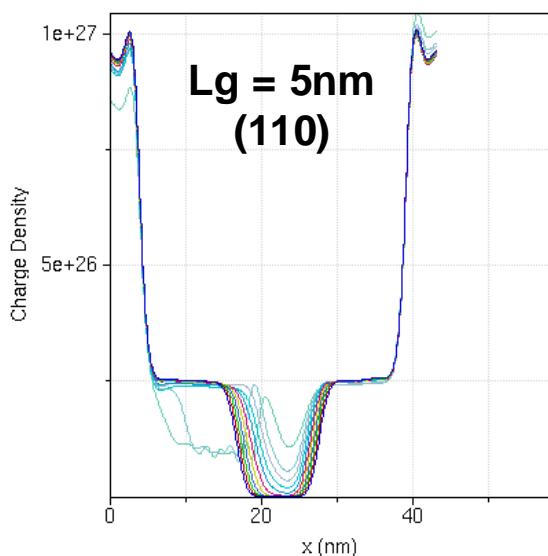

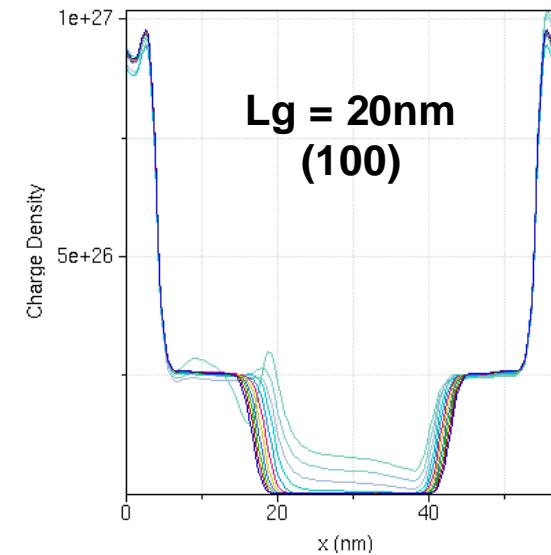

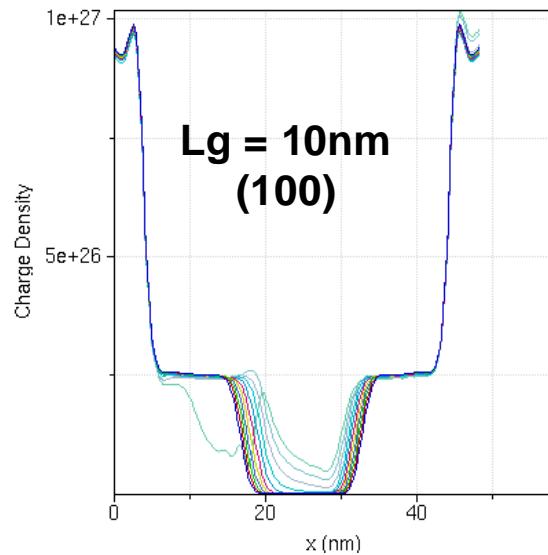

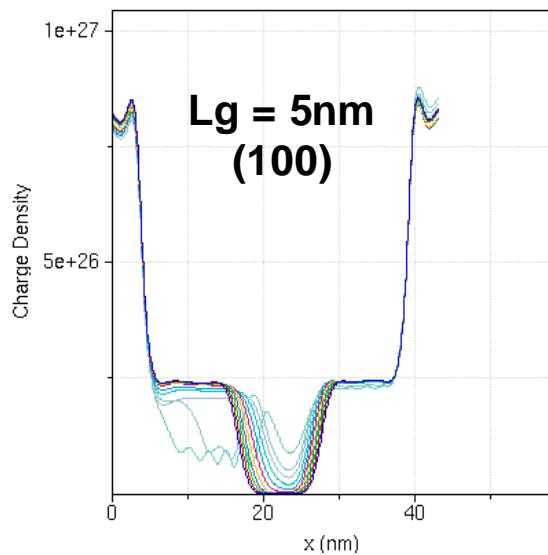

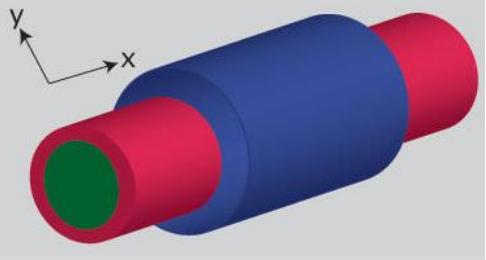

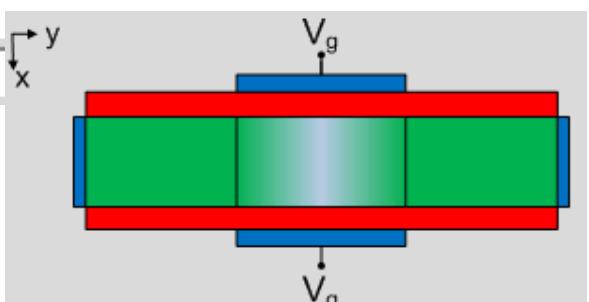

# Fast Nanowire Quantum Transport

## Objective:

- Explore Fully Quantum Mechanical Transport Calculation

## Problem:

- Modeling 3nm Gate-all-around nanowires

## Results / Impact:

- Gate-all-around nanowire provides better electrostatic gate control over channel

- Even for a Gate Length as short as 5nm, Off current is significantly low  $\Rightarrow$  better  $I_{ON}/I_{OFF}$

- Charge profiles across Gate lengths and Crystal direction shown in Appendix (Charge Density Profiles)

## Approach:

- 3nm Gate-all-around nanowires were modeled using Multi-gate Nanowire FET tool on nanoHub.

- Effects of varying Gate length (5nm, 10nm, 20nm) in 2 different crystal directions studied

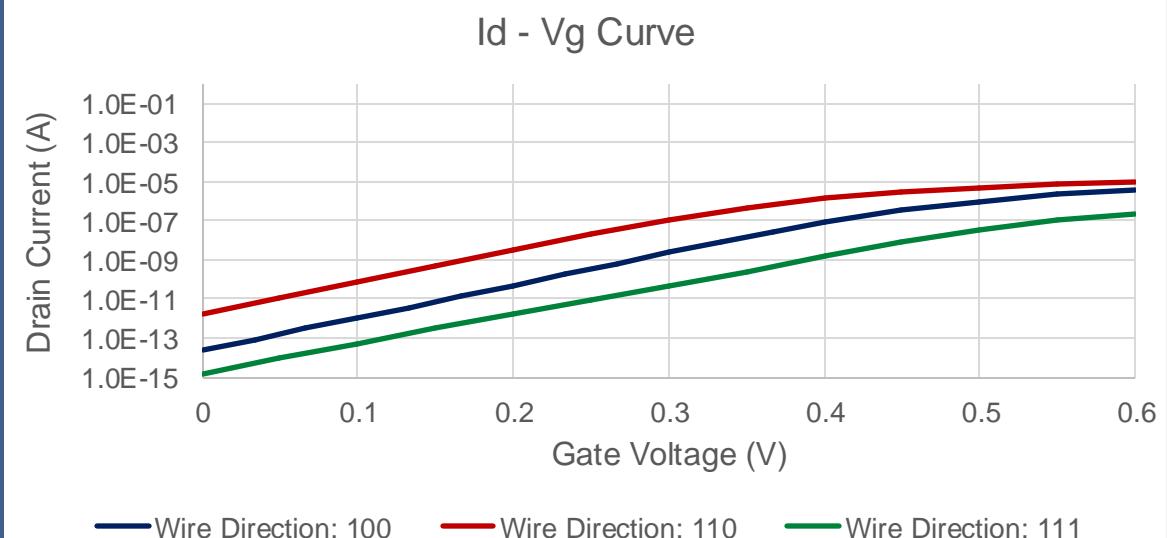

# Long Nanowire Quantum Transport (Quad Chart 1 of 2)

## Objective:

- Understand atomistic quantum transport through 2.1nm cross section nanowires using a gate and channel length of 15nm.

## Problem:

- What are the general features of the I-V curves of 100, 110, and 111 wire directions?

## Approach:

- A silicon nanowire was modeled in NanoHub's Omenwire tool, varying the nanowire transport direction.

- Please see [NanoHub Inputs](#) (located in the Appendix) for the inputs used in this simulation.

## Results / Impact:

- Shown below on the logarithmic plot, the drain current is the greatest in the 110 direction and lowest in the 111 direction.

- All directions start to slow their increase in current between 0.35V and 0.55V.

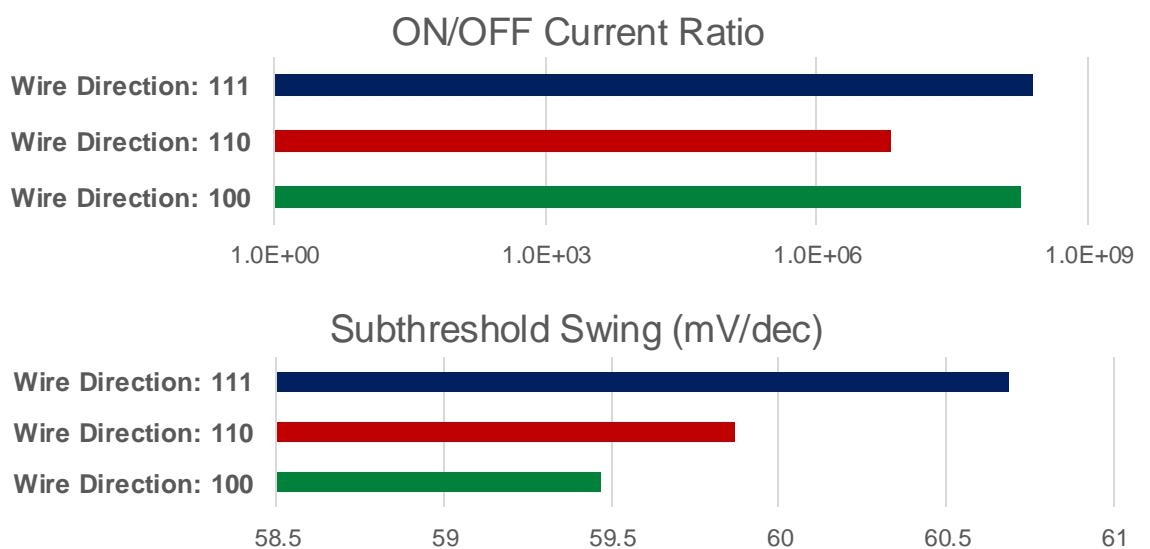

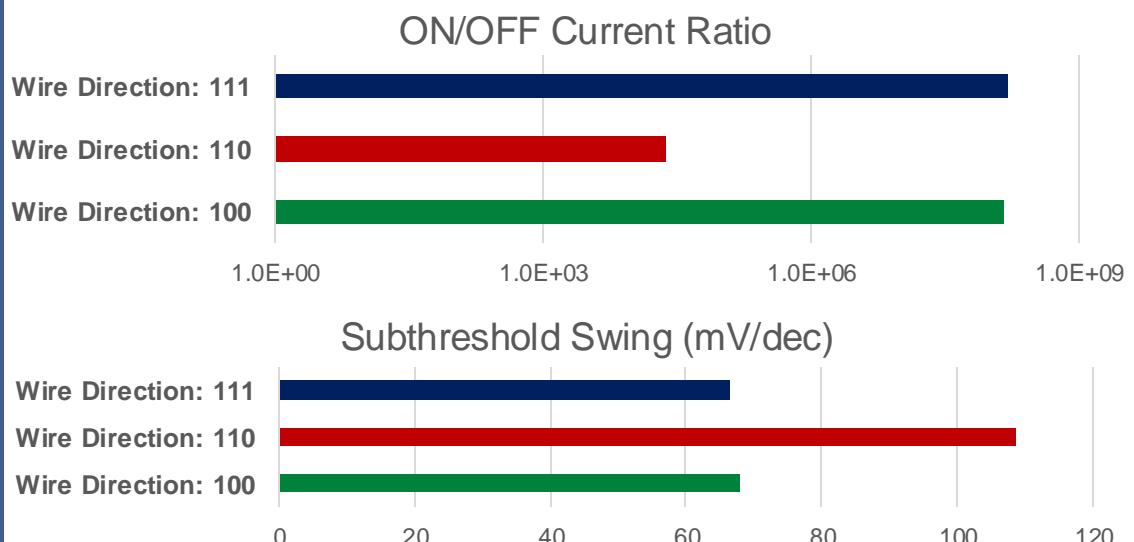

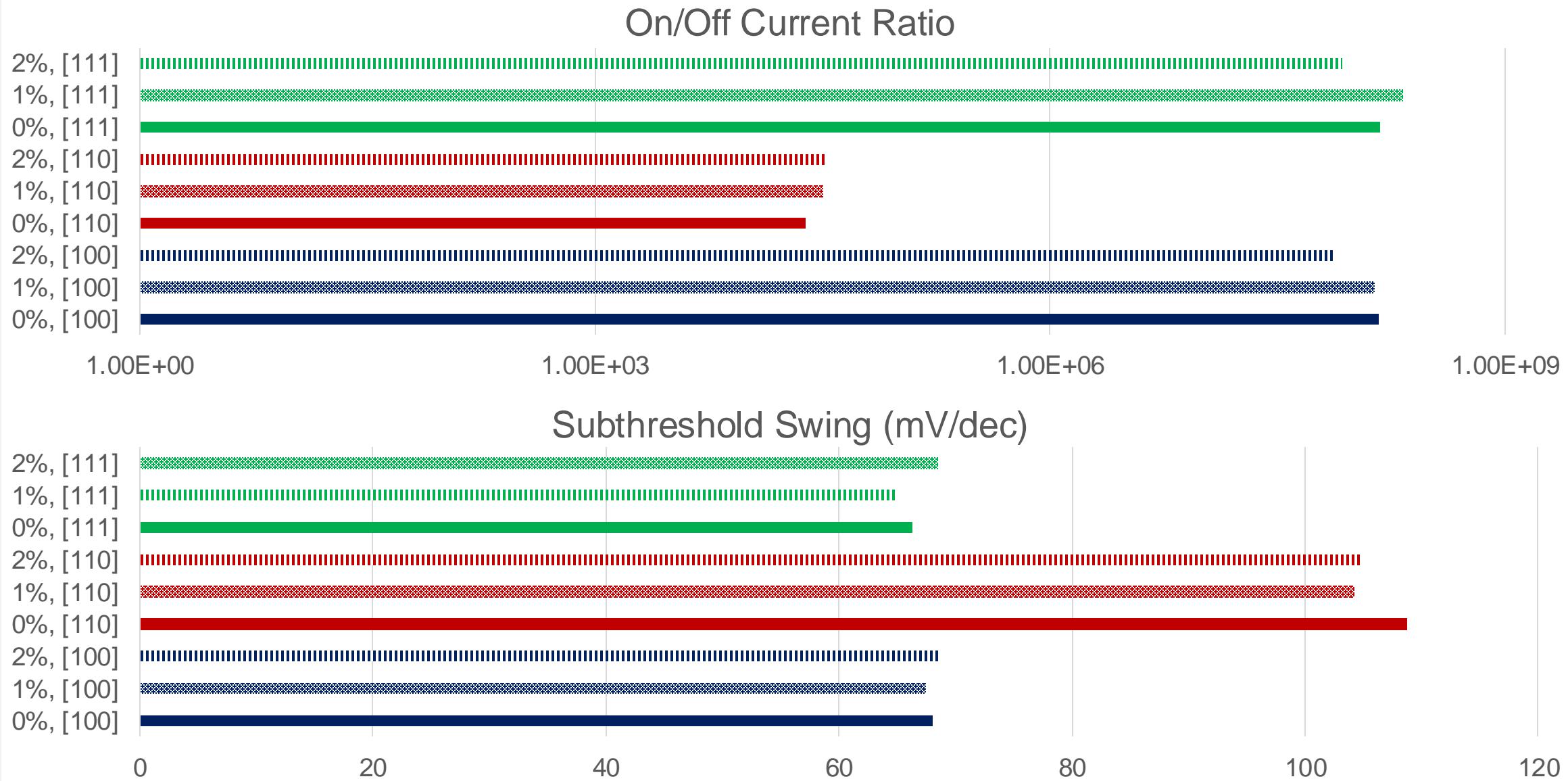

# Long Nanowire Quantum Transport (Quad Chart 2 of 2)

## Objective:

- Understand atomistic quantum transport through 2.1nm cross section nanowires using a gate and channel length of 15nm.

## Problem:

- How do the subthreshold swings and On/Off current ratios differ between 100, 110, and 111 wire directions?

## Approach:

- A silicon nanowire was modeled in NanoHub's Omenwire tool, varying the nanowire transport direction.

- Please see [NanoHub Inputs](#) (located in the Appendix) for the inputs used in this simulation.

## Results / Impact:

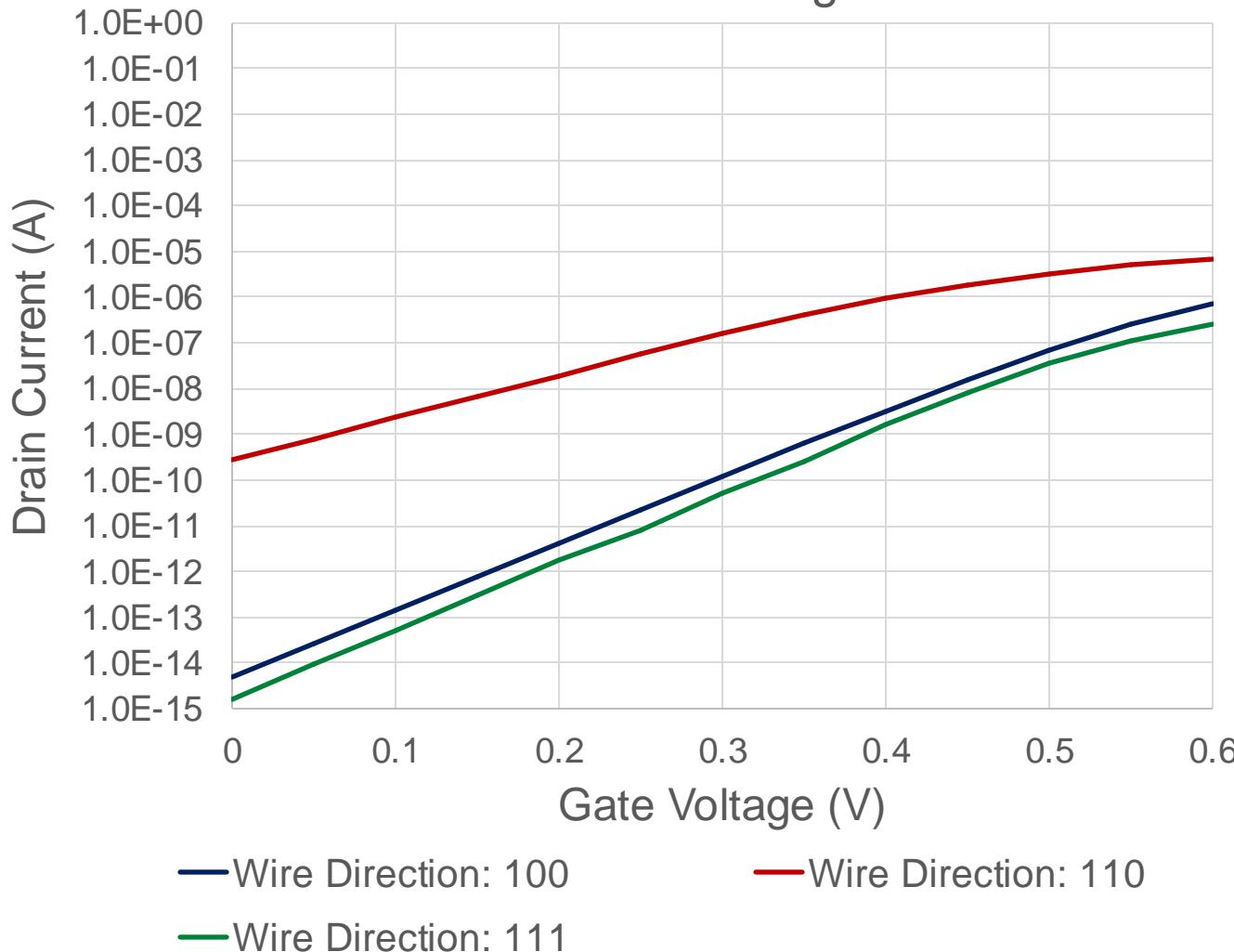

- The On/Off current ratio in the 110 direction is drastically smaller than the others.

- The subthreshold swing however has a linear change between the 100, 110, and 111 direction, steadily increasing.

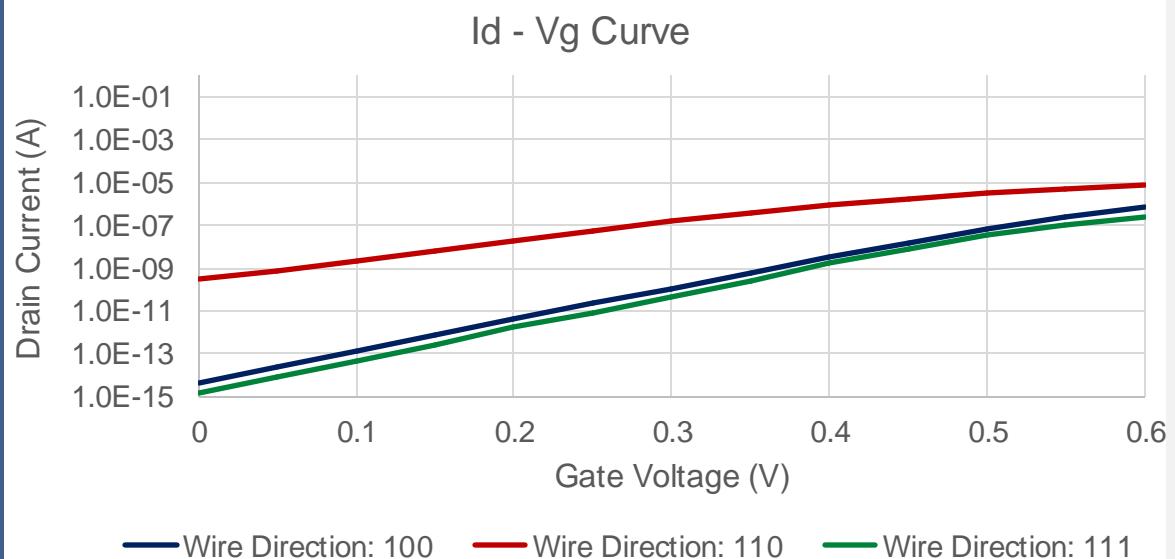

# Short Nanowire Quantum Transport (Quad Chart 1 of 2)

## Objective:

- Understand atomistic quantum transport through 1.9nm cross section nanowires using a gate and channel length of 5nm.

## Problem:

- What are the general features of the I-V curves of 100, 110, and 111 wire directions?

## Approach:

- A silicon nanowire was modeled in NanoHub's Omenwire tool, varying the nanowire transport direction.

- Please see [NanoHub Inputs](#) (located in the Appendix) for the inputs used in this simulation.

## Results / Impact:

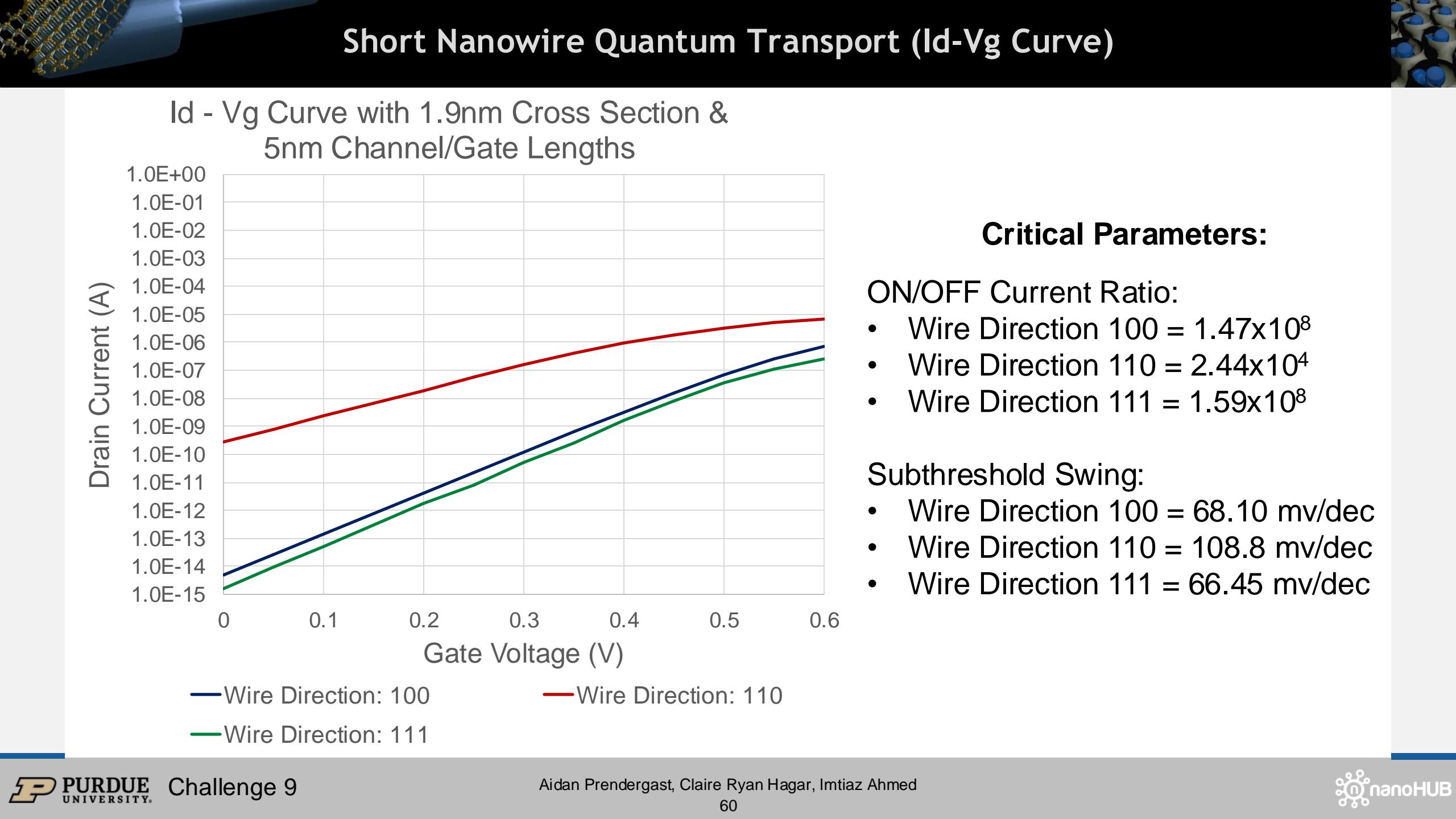

- Shown below on the logarithmic plot, the drain current is the greatest in the 110 direction and lowest in the 111 direction.

- The current is very similar in the 100 and 111 directions.

- All directions don't start to slow their increase in current until after 0.55V.

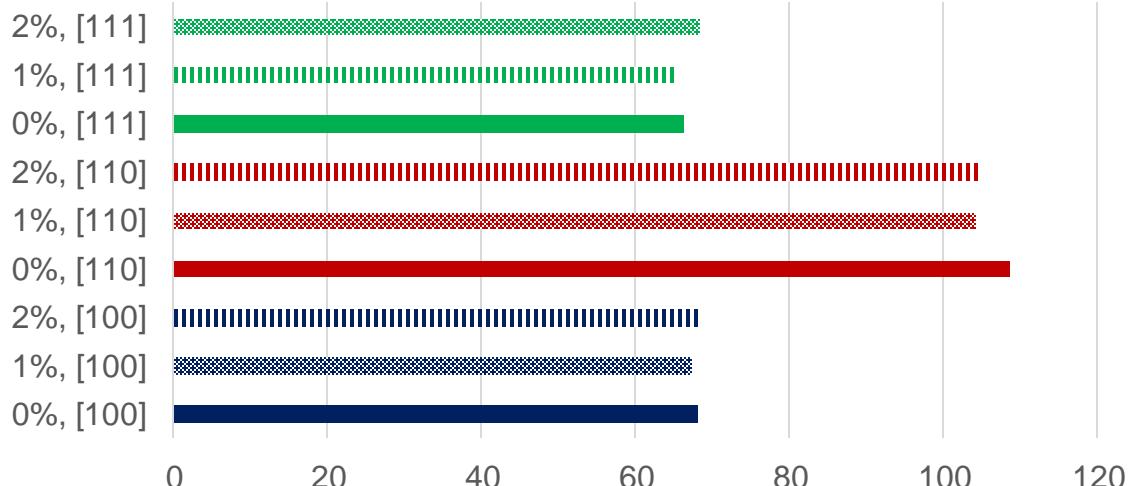

# Short Nanowire Quantum Transport (Quad Chart 2 of 2)

## Objective:

- Understand atomistic quantum transport through 1.9nm cross section nanowires using a gate and channel length of 5nm.

## Problem:

- How do the subthreshold swings and On/Off current ratios differ between 100, 110, and 111 wire directions?

## Approach:

- A silicon nanowire was modeled in NanoHub's Omenwire tool, varying the nanowire transport direction.

- Please see [NanoHub Inputs](#) (located in the Appendix) for the inputs used in this simulation.

## Results / Impact:

- The On/Off current ratio did not significantly change between the long and short nanowire.

- The subthreshold swing did show a large difference. With the short nanowire, the 110 direction showed a large increase.

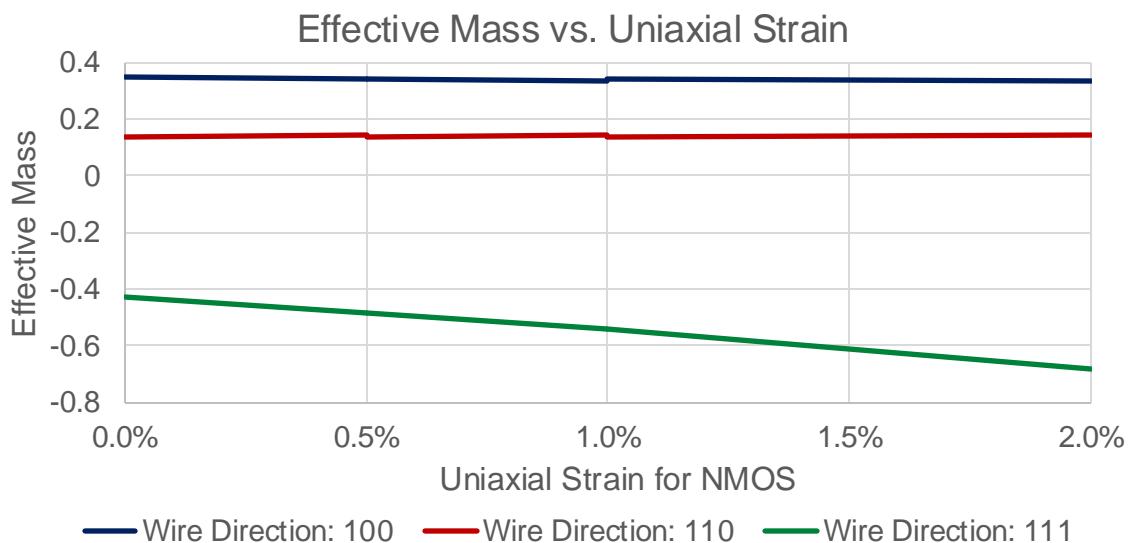

# Nanowire Dispersion Design (Quad Chart 1 of 2)

## Objective:

- Understand what inputs can be used to increase the performance of a nanowire.

## Problem:

- How can the nanowire be tuned to better the transistor performance?

## Results / Impact:

- The effective mass ( $m^*$ ) is defined as the inverse of the second derivative of  $E-k$  times the square of Plank's constant.

- $m^*$  varies inversely with the sharpness, or curvature, of the bands. This is decreased by increasing the strain (shown below).

## Approach:

- A silicon nanowire was modeled in NanoHub's BandstructureLab tool, varying the uniaxial strain from 0%, 0.5%, 1%, & 2%.

- Please see [NanoHub Inputs](#) (located in the Appendix) for the inputs used in this simulation.

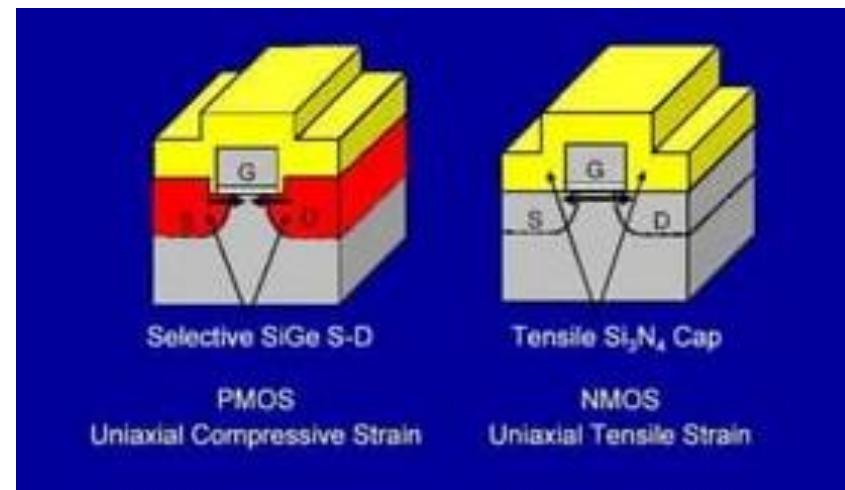

# Nanowire Dispersion Design (Quad Chart 2 of 2)

## Objective:

- Understand what inputs can be used to increase the performance of a nanowire.

## Problem:

- What kinds of strain is associated with transistors? What is reasonable to do with nanowires?

## Approach:

- Various publications were researched for what kind of strain is associated with transistors.

- Please see [Resources](#) 2 – 5 (located in the Appendix) for the list of publications reviewed.

## Results / Impact:

- Each publication reviewed concluded that NMOS transistors should be stretched to enhance electron mobility.

- PMOS transistors should be compressed to enhance hole mobility.

- Also noted, using two separate crystal directions would be most optimal, but it is not realistic outside of a simulation.

[3]

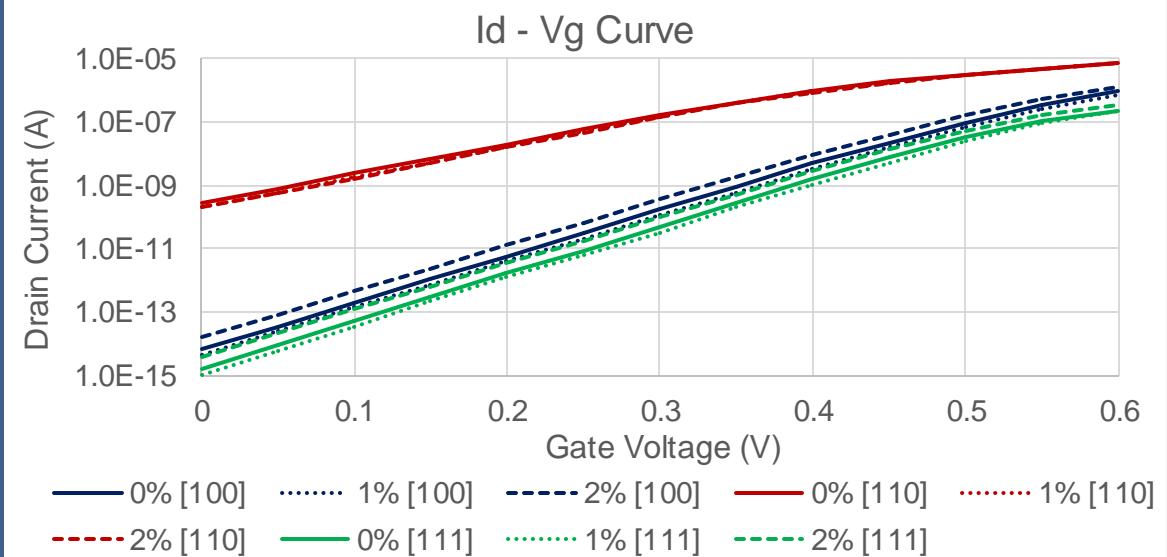

# Optimized Nanowire Quantum Transport (Quad Chart 1 of 2)

## Objective:

- Understand how changes to a transistor impact performance.

## Problem:

- How did the changes implemented in Challenge #10 impact the performance of the transistor?

## Approach:

- A silicon nanowire was modeled in NanoHub's Omenwire tool, varying the uniaxial strain from 0%, 1%, & 2%.

- Please see [NanoHub Inputs](#) (located in the Appendix) for the inputs used in this simulation.

## Results / Impact:

- Shown below and in [Id-Vg Curve](#) (located in the Appendix) in greater detail, there is not a significant difference between the I-V curves for various uniaxial strains.

# Optimized Nanowire Quantum Transport (Quad Chart 2 of 2)

## Objective:

- Understand how changes to a transistor impact performance.

## Problem:

- What other improvements could be made to better the performance?

## Results / Impact:

- The subthreshold swing (shown below) and the on/off current ratio (shown in the Appendix, [Critical Parameters](#)) demonstrate the best performance will occur at 1% strain (compared to 0% or 2%).

## Approach:

- A silicon nanowire was modeled in NanoHub's Omenwire tool, varying the uniaxial strain from 0%, 1%, & 2%.

- Please see [NanoHub Inputs](#) (located in the Appendix) for the inputs used in this simulation.

Subthreshold Swing (mV/dec)

# Hole Nanowire Bandstructure (Quad Chart 1 of 2)

## Objective:

- Understand the hole bandstructure in nanowires.

## Problem:

- How does the mass at Gamma Point ( $k=0$ ) change as a function of the wire diameter?

## Results / Impact:

- Shown below, for wire directions 110 and 111, the mass at the Gamma point does not have a significant change.

- For wire direction 100, the mass decreases at the Gamma point.

- There are peaks off the Gamma point of -0.524, -0.722, and -0.518 for 2.1nm, 4nm, and 6nm diameters respectively.

## Approach:

- A silicon nanowire was modeled in NanoHub's BandstructureLab tool, varying the wire diameter from 2.1nm, 4nm, 6nm, and 8nm.

- Please see [NanoHub Inputs](#) (located in the Appendix) for the inputs used in this simulation.

# Hole Nanowire Bandstructure (Quad Chart 2 of 2)

## Objective:

- Understand the hole bandstructure in nanowires.

## Problem:

- Which wire direction is recommended at a diameter of 2.1mm?

## Results / Impact:

- There are degeneracies at diameters  $> 2.1\text{nm}$ .

- The best wire direction for a 2.1nm diameter wire is in the 100 direction, due to the decreased mass.

## Approach:

- A silicon nanowire was modeled in NanoHub's BandstructureLab tool, varying the wire diameter from 2.1nm, 4nm, 6nm, and 8nm.

- Please see [NanoHub Inputs](#) (located in the Appendix) for the inputs used in this simulation.

# What We Learned

- Short Channel effects occur when Channel length is comparable to Source/Drain depletion width

- More pronounced in Planar MOSFETs

- Hampers device performance with scaling

- Nanowires with Gate-all-around structure restore device performance with Excellent Electrostatic Gate control over the channel.

- On/Off Current ratio, Subthreshold Swing, Effect of strain across various Gate lengths and Nanowire Diameters along with other conditions studied, and Id-Vg characteristics investigated to model Nanowire Transistors

## To Conclude

- Transistors number in the billions in individual devices that we use everyday

- You likely care about how powerful your phone is and how long its battery lasts!

- Nanowire transistors allow us to create more ideal devices for lower power and better performance

- Utilizing the design levers discussed here allows us to design the best application-specific transistors possible

- We've shown here how Nanowires outperform Planar Transistors in

- » Leakage Currents

- » On/Off Current Ratio

- » Subthreshold Swing

- » Drain-Induced-Barrier-Lowering

- Nanowire scale allows their density to continue increasing

- Nanowires look to usher in a new era of performance and efficiency!

# Appendices

## Team “Electron Highway”

- This team consisted of three members with distinct backgrounds split between academic research and industry experience.

- The team effort focused on collaboration rather than a division of labor.

- To build a basis for this project, every member attempted Challenge 1, 2, & 3 and collaborated on the final solution.

- All other challenges had at least two members, with members choosing challenges they were particularly interested in or had a background in. The team collaborated on the final solution.

- Utilized meetings to discuss final solutions and shared messaging app to collaborate when "stuck" on a problem

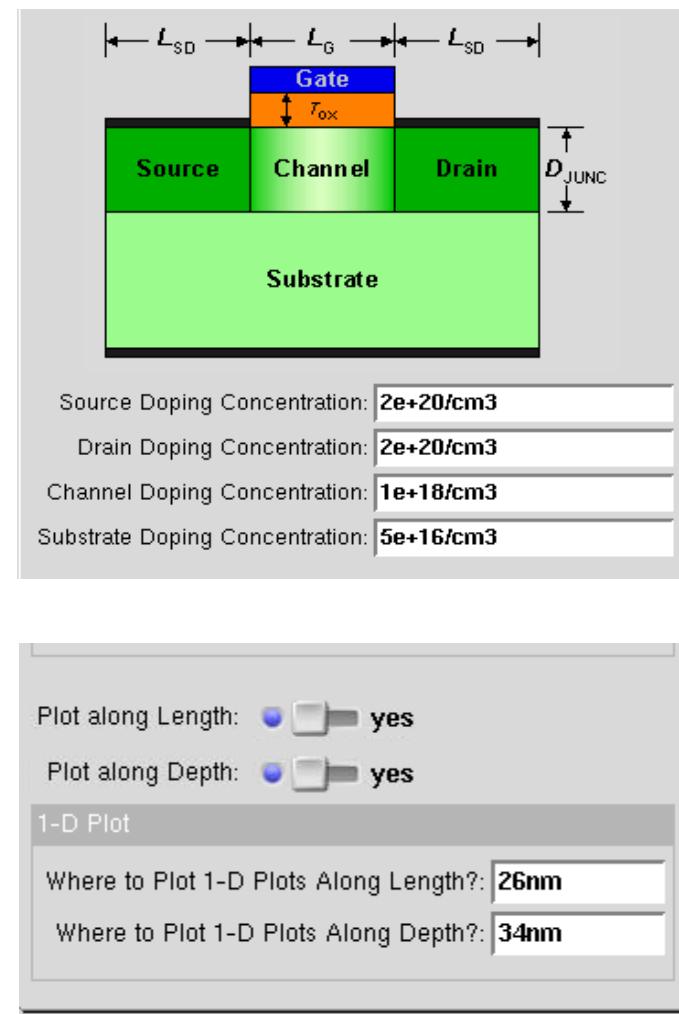

# Classical MOSFET Limitations (NanoHub MOSFET Inputs)

Structural Properties | Model | Voltage Sweep |

Device Type: MOSFET n-type

Doping Profile: Uniform Doping Density

Source/Drain Length:  30nm

Source/Drain Nodes:  15

Channel Length:  150nm

Channel Nodes:  22

Oxide Thickness:  0.8nm

Oxide Nodes:  5

Junction Depth:  9nm

Junction Nodes:  30

Substrate Thickness:  18nm

Substrate Nodes:  10

Device Width:  1000nm

I-Vg Plot

Plot Transfer Characteristic:  yes

Vg Minimum:  0V

Vg Maximum:  0.6V

Number of Points:  30

Vd Bias Minimum:  0.05V

Vd Bias Maximum:  0.6V

Number of Curves:  2

Vb Bias Point:  0V

I-Vd Plot

Plot I-Vd Characteristic:  no

Vd Minimum:  0V

Vd Maximum:  1.2V

Number of Points:  15

Vg Bias Minimum:  0.5V

Vg Bias Maximum:  1.2V

Number of Curves:  3

Vb Bias Point:  0V

Tool located at:

<https://nanohub.org/tools/mosfet>

# Classical MOSFET Limitations (Voltage Potentials)

# Classical MOSFET Limitations (Electron Densities)

Electron Density vs Cross Section Length Over Gate Lengths (nm)

Electron Density vs Gate Length Over Cross Section Lengths ( $\mu\text{m}$ )

# Classical MOSFET Limitations (Transistor Features)

Note, due to the increasingly high leakage currents at low channel lengths, 10nm and 5nm subthreshold swing values were excluded from the above plot.

# Classical MOSFET Limitations (Transistor Features)

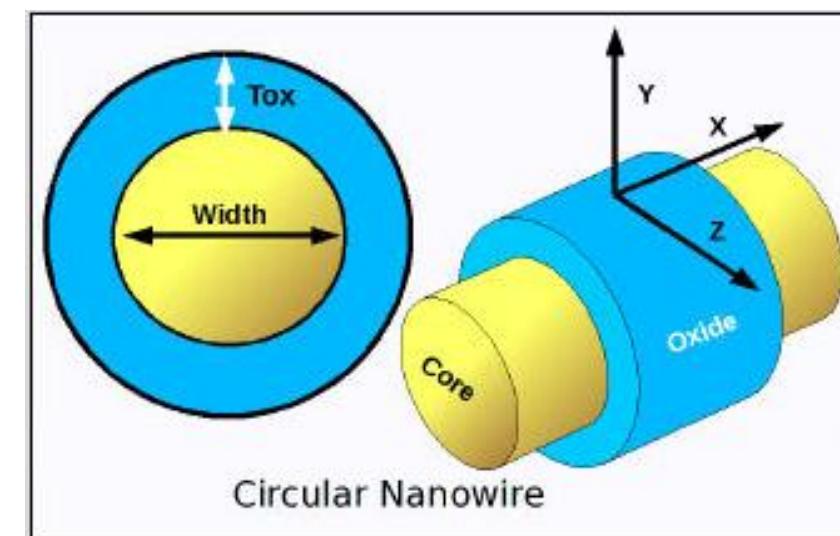

# Nanowire with Drift Diffusion (NanoHub NANOFINFET Inputs)

All default settings were utilized, except as where shown (red boxes mark variable inputs):

Device Type

Class: Nanowire

Spec

Gate Type: Metal

Geometry-X

Gate Contact

Oxide

Wire

Source Extension

Drain Extension

Geometry-Y

Geometry-Z

Doping

Gaussian doping

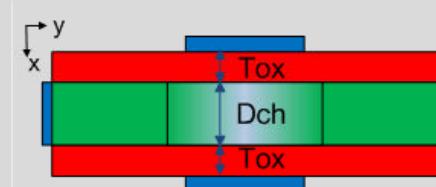

Geometry-X

Tox

Dch

Tox

Diameter - Dch: **2.1nm**

Oxide thickness - Tox: **2.5nm**

Channel width - Wch: **30nm**

Oxide thickness 1 - Tox1: **2.5nm**

Oxide thickness 2 - Tox2: **2.5nm**

Substrate - S: **100nm**

Geometry-Y

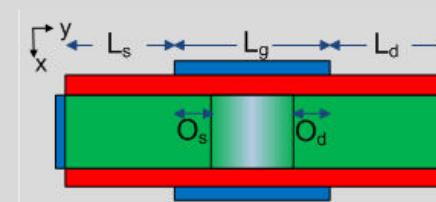

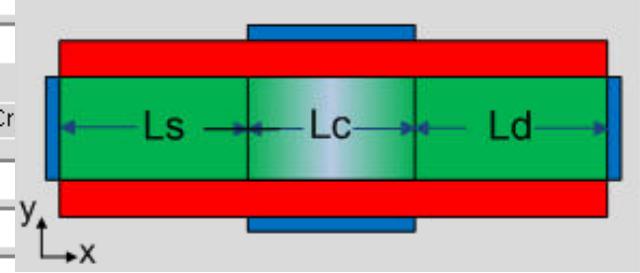

**L<sub>s</sub>** **L<sub>g</sub>** **L<sub>d</sub>**

**O<sub>s</sub>** **O<sub>d</sub>**

Gate length - L<sub>g</sub>: **20nm**

Source extension length - L<sub>s</sub>: **20nm**

Drain extension length - L<sub>d</sub>: **20nm**

Gate overlap to source - O<sub>s</sub>: **2nm**

Gate overlap to drain - O<sub>d</sub>: **2nm**

Spacer: **15nm**

Tool located at:

<https://nanohub.org/tools/nanofinfet>

# Nanowire with Drift Diffusion (Subthreshold Swing)

# Nanowire with Drift Diffusion (On/Off Current Ratio)

# Nanowire with Drift Diffusion (Threshold Voltage)

# Nanowire with Drift Diffusion (Energy)

Energy vs. Gate Lengths Over Nanowire Diameters (nm)

Energy vs. Gate Lengths Over Nanowire Diameters (nm) - Zoomed

# Nanowire with Drift Diffusion - Workfunction Variations and Gate Potential Analysis (Transistor Parameters)

# Nanowire with Drift Diffusion - Workfunction Variations and Gate Potential Analysis (Energy)

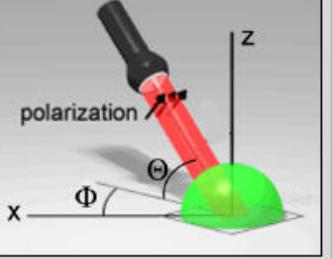

# Nanowire Modes and Gating (NanoHub Quantum Dot Lab Inputs)

Quantum Dot Structure

Type of Quantum Dot Structure: Simple Quantum Dot

Simple Quantum Dot Options

Shape: Cylinder

Number of States: 8

X Dimensions: 2nm

Y Dimensions: 2nm

Z Dimensions: 1nm

Lattice Constant: 0.5nm

Effective Mass: .91

Energy gap: 1.43eV

Light Incident Angles

Angle Theta: 45deg

Angle Phi: 0deg

Sweep

Sweep Parameter: Angle phi (deg)

Minimum: 0

Maximum: 90

Number of Points: 3

Absorption

Simple Q Dot - Absolute Fermi Level: no

Simple Q Dot - Rel. or Abs. Fermi Level: 0eV

Multi-Layer - Fermi Level: 0.7eV

Temperature: 300K

State Broadening: 0.001

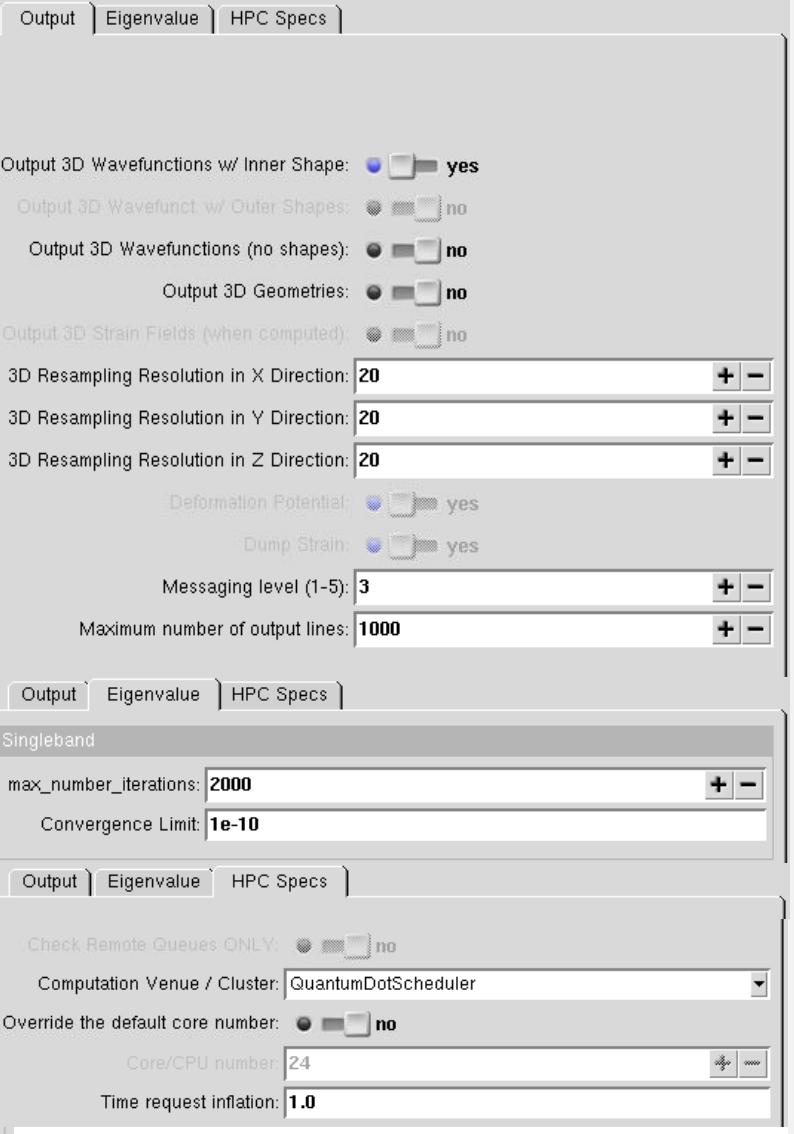

Output Eigenvalue HPC Specs

Output 3D Wavefunctions w/ Inner Shape: yes

Output 3D Wavefunct. w/ Outer Shapes: no

Output 3D Wavefunctions (no shapes): no

Output 3D Geometries: no

Output 3D Strain Fields (when computed): no

3D Resampling Resolution in X Direction: 20

3D Resampling Resolution in Y Direction: 20

3D Resampling Resolution in Z Direction: 20

Deformation Potential: yes

Dump Strain: yes

Messaging level (1-5): 3

Maximum number of output lines: 1000

Output Eigenvalue HPC Specs

Singleband

max\_number\_iterations: 2000

Convergence Limit: 1e-10

Output Eigenvalue HPC Specs

Check Remote Queues-ONLY: no

Computation Venue / Cluster: QuantumDotScheduler

Override the default core number: no

Core/CPU number: 24

Time request inflation: 1.0

Tool located at:

<https://nanohub.org/tools/qdot>

# Nanowire Modes and Gating (Wavefunctions)

Effective Mass: 0.19

Effective Mass: 0.91

# Nanowire Modes and Gating (Eigen Energies)

Effective Mass: 0.19

Effective Mass: 0.91

# Nanowire Modes and Gating (NanoHub Nanowire Inputs)

Simulation parameters

Transport model: Uncoupled mode space NEGF

Include scattering:  no

Number of eigenvalues: 9

Mesh fineness factor: 7

Geometry & doping | Gate | Drain |

Diameter of the silicon-nanowire: 2nm

Oxide thickness: 1nm

Gate length: 8nm

Source & drain extension length: 8nm

Source & drain doping (n) in:  $1e+20/cm^3$

Geometry & doping | Gate | Drain |

Gate voltage start value: 0V

Step size: 0.04V

Number of steps: 11

Geometry & doping | Gate | Drain |

Drain voltage start value: 0.4V

Step size: 0.001V

Number of steps: 1

Material Properties

Simulation materials: Silicon(Si)

Gate work function: 4.05eV

Orientation: 1 1 1

Tool located at:

<https://nanohub.org/tools/nanowire>

# Nanowire Modes and Gating (I-Vg Curves)

Crystal Direction: 110

Crystal Direction: 111

# Nanowire Modes and Gating (1D Electron Densities)

# Nanowire Modes and Gating (3D Electron Densities)

Crystal

Direction: 110

Crystal

Direction: 111

# Nanowire Realistic Bandstructure (Inputs)

All default settings were utilized, except as where shown (red boxes mark variable inputs):

1 Device Type → 2 Physics → 3 K-Space → 4 Numerics → 5 Simulate

Geometry: Nanowire (1D-periodic)

Calculation For: Electrons

Material: Si

Alloy Model: Virtual Crystal Approximation

Molar fraction: 0.5

Job Type: Calculate the wire band structure

Device cross section: Circle

Diameter: **2.1nm**

Oxide Thickness( $T_{ox}$ ): 2.2nm

Crystal Orientation

Transport direction (X): **(100)**

Confinement direction (Z): [010]

Tool located at:

<https://nanohub.org/resources/bandstrlab>

# Nanowire Realistic Bandstructure (Masses)

# Nanowire Realistic Bandstructure (Degeneracies)

| Diameter (nm) | Region       | (100) direction  |            | (110) direction  |            | (111) direction  |            |

|---------------|--------------|------------------|------------|------------------|------------|------------------|------------|

|               |              | $m_{\text{eff}}$ | Degeneracy | $m_{\text{eff}}$ | Degeneracy | $m_{\text{eff}}$ | Degeneracy |

| 2.1           | <b>Gamma</b> | 0.346            | 3          | 0.107            | 2          | 0.56             | 2          |

|               | <b>Delta</b> | 0.963            | 1          | 0.616            | 2          | 0.698            | 2          |

| 5             | <b>Gamma</b> | 0.236            | 4          | 0.180            | 2          | 0.45             | 4          |

|               | <b>Delta</b> | 0.898            | 1          | 0.556            | 2          | 0.423            | 2          |

| 10            | <b>Gamma</b> | 0.211            | 3          | 0.196            | 3          | 0.43             | 2          |

|               | <b>Delta</b> | 0.905            | 1          | 0.52             | 3          | 0.416            | 2          |

Number of Degeneracies vs. Diameter

# Nanowire Top-of-Barrier Transport (Inputs)

All default settings were utilized, except as where shown (red boxes mark variable inputs):

Device   Models   Environment

Model: Silicon Nanowire MOSFET

Nanowire Diameter: **2.1nm**

Gate Insulator Thickness: **1.5nm**

Gate Insulator Dielectric Constant: **3.9**

Transport Effective Mass: **.346**

Valley Degeneracy: **3** **+** **-**

Threshold Voltage: **0.32V**

Gate Control Parameter: **1**

Drain Control Parameter: **0**

Series Resistance (ohm- $\mu$ m): **0**

Ambient Temperature: **300K**

Gate Voltage Sweep

Initial Gate Voltage: **0V**

Final Gate Voltage: **1V**

Gate Voltage Bias Points: **13** **+** **-**

Drain Voltage Sweep

Initial Drain Voltage: **0V**

Final Drain Voltage: **1V**

Drain Voltage Bias Points: **13** **+** **-**

Tool located at:

<https://nanohub.org/resources/fettoy>

# Nanowire Top-of-Barrier Transport (I-V Curves)

# Fast Nanowire Quantum Transport (Input Deck)

Lsd : Source/Drain Length:  **20nm**

Lc : Channel Length:  **3nm**

Lg : Gate Length:  **5nm** → Varied across 5nm, 10nm, 20nm

Tox : Oxide Thickness:  **1nm**

Tsi : Silicon Body Thickness:  **3nm**

Tbox : Buried Oxide Thickness:  **1nm**

Wox : Oxide Width:  **1nm**

Wsi : Silicon Body Width:  **3nm**

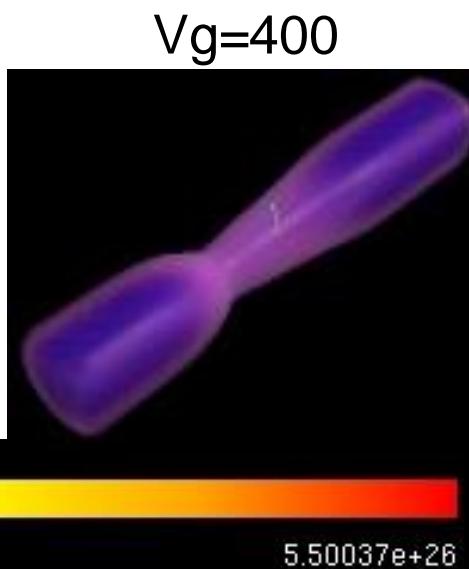

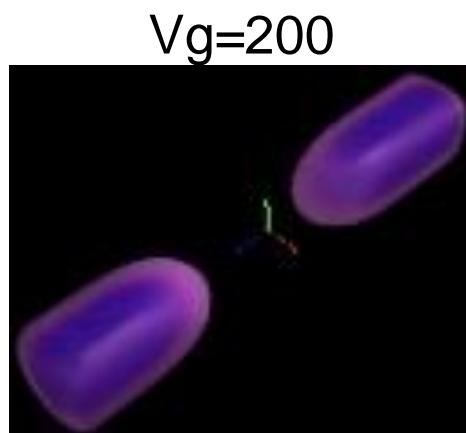

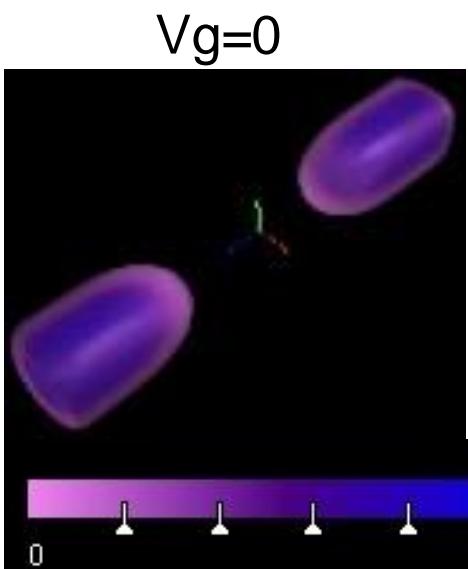

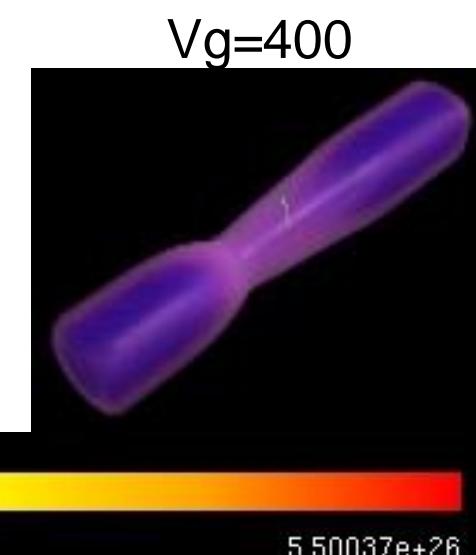

# Fast Nanowire Quantum Transport (Charge Density Profiles)

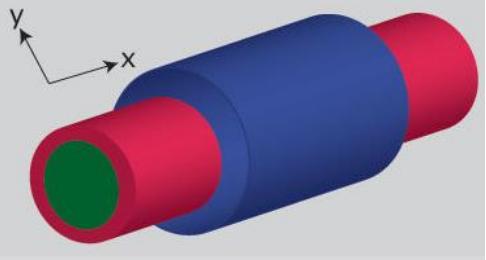

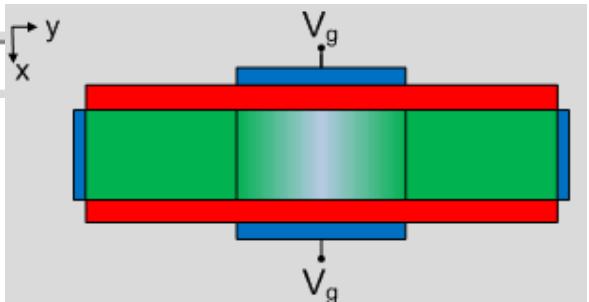

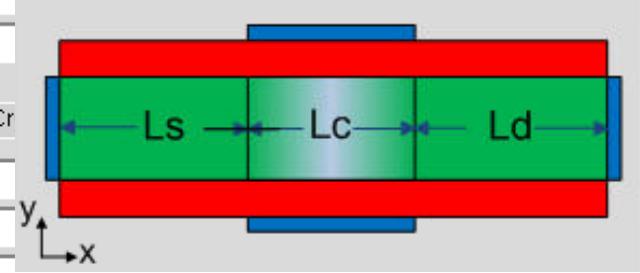

# Long Nanowire Quantum Transport (Inputs)

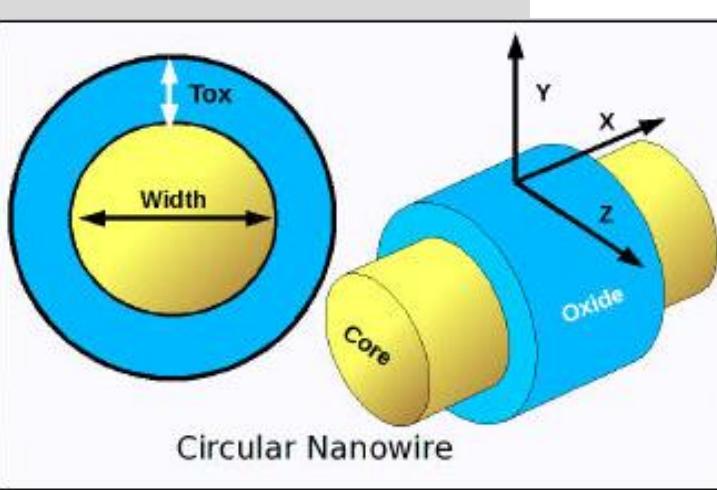

1 Device Type → 2 Structure → 3 Material → 4 Environments → 5 Expert Options

Device Type

Class: Circular Nanowire

1 Device Type → 2 Structure → 3 Material → 4 Environments → 5 Expert Options

Plot options for bias Gate bias Drain bias Source bias Temperature

Minimum bias:  0V

Maximum bias:  0.6V

Number of bias points:  13

1 Device Type → 2 Structure → 3 Material → 4 Environments → 5 Expert Options

Geometry-X Geometry-Y Geometry-Z Crystal Orientation Strain Doping

Channel length - Lc:  15nm

Source length - Ls:  10nm

Drain length - Ld:  10nm

Geometry-X Geometry-Y Geometry-Z Cr...

Diameter - Dch:  2.1nm

Oxide thickness - Tox:  1nm

Channel width - Wch:  2.5nm

Left wall oxide thickness - Tox1:  1nm

Right wall oxide thickness - Tox2:  1nm

Geometry-X Geometry-Y Geometry-Z Crystal Orientation Strain Doping

Transport direction:  1 1 1

Confinement direction in y:  -1 1 0

Confinement direction in z:  -1 -1 2

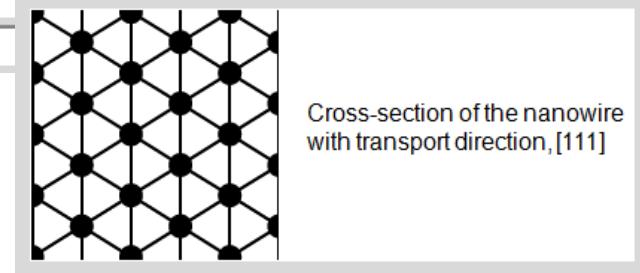

Cross-section of the nanowire with transport direction, [111]

Tool located at:

<https://nanohub.org/resources/omenwire>

# Long Nanowire Quantum Transport (Id-Vg Curve)

Id - Vg Curve with 2.1nm Cross Section &

15nm Channel/Gate Lengths

## Critical Parameters:

ON/OFF Current Ratio:

- Wire Direction 100 =  $1.86 \times 10^8$

- Wire Direction 110 =  $6.77 \times 10^6$

- Wire Direction 111 =  $2.46 \times 10^8$

Subthreshold Swing:

- Wire Direction 100 = 59.47 mv/dec

- Wire Direction 110 = 59.87 mv/dec

- Wire Direction 111 = 60.69 mv/dec

# Short Nanowire Quantum Transport (Inputs)

1 Device Type → 2 Structure → 3 Material → 4 Environments → 5 Expert Options

Device Type

Class: Circular Nanowire

1 Device Type → 2 Structure → 3 Material → 4 Environments → 5 Expert Options

Plot options for bias Gate bias Drain bias Source bias Temperature

Minimum bias:  $-1\pm 0V$

Maximum bias:  $-1\pm 0.6V$

Number of bias points: 13

1 Device Type → 2 Structure → 3 Material → 4 Environments → 5 Expert Options

Geometry-X Geometry-Y Geometry-Z Crystal Orientation Strain Doping

Channel length - Lc: 15nm

Source length - Ls: 10nm

Drain length - Ld: 10nm

Geometry-X Geometry-Y Geometry-Z Cr Strain Doping

Diameter - Dch: 1.9nm

Oxide thickness - Tox: 1nm

Channel width - Wch: 2.5nm

Left wall oxide thickness - Tox1: 1nm

Right wall oxide thickness - Tox2: 1nm

Transport direction: 1 1 1

Confinement direction in y: -1 1 0

Confinement direction in z: -1 -1 2

Tool located at:

<https://nanohub.org/resources/omenwire>

# Short Nanowire Quantum Transport (Id-Vg Curve)

Id - Vg Curve with 1.9nm Cross Section &

5nm Channel/Gate Lengths

## Critical Parameters:

ON/OFF Current Ratio:

- Wire Direction 100 =  $1.47 \times 10^8$

- Wire Direction 110 =  $2.44 \times 10^4$

- Wire Direction 111 =  $1.59 \times 10^8$

Subthreshold Swing:

- Wire Direction 100 = 68.10 mv/dec

- Wire Direction 110 = 108.8 mv/dec

- Wire Direction 111 = 66.45 mv/dec

# Nanowire Dispersion Design (Inputs)

All default settings were utilized, except as where shown:

1 Device Type → 2 Physics → 3 K-Space → 4 Numerics → 5 Simulate

Geometry: Nanowire (1D-periodic)

Calculation For: Electrons

Material: Si

Alloy Model: Virtual Crystal Approximation

Molar fraction: 0.5

Job Type: Calculate the wire band structure

Device cross section: Circle

Diameter: 1.9nm

Oxide Thickness( $T_{ox}$ ): 2.2nm

Crystal Orientation

Transport direction (X): (100)

Confinement direction (Z): [010]

1 Device Type → 2 Physics → 3 K-Space → 4 Numerics → 5 Simulate

Electronic Structure   Strain

Strain type: Uniaxial (along transport direction X)

Epsilon: 0.02

Tool located at:

<https://nanohub.org/resources/bandstrlab>

# Optimized Nanowire Quantum Transport (Inputs)

1 Device Type → 2 Structure → 3 Material → 4 Environments → 5 Expert Options

Device Type

Class: Circular Nanowire

1 Device Type → 2 Structure → 3 Material → 4 Environments → 5 Expert Options

Plot options for bias Gate bias Drain bias Source bias Temperature

Minimum bias:  0V

Maximum bias:  0.6V

Number of bias points:  13

1 Device Type → 2 Structure → 3 Material → 4 Environments → 5 Expert Options

Geometry-X Geometry-Y Geometry-Z Crystal Orientation Strain Doping

Channel length - Lc:  15nm

Source length - Ls:  10nm

Drain length - Ld:  10nm

Geometry-X Geometry-Y Geometry-Z Cr Strain Doping

Diameter - Dch:  1.9nm

Oxide thickness - Tox:  1nm

Channel width - Wch:  2.5nm

Left wall oxide thickness - Tox1:  1nm

Right wall oxide thickness - Tox2:  1nm

Geometry-X Geometry-Y Geometry-Z Crystal Orientation Strain Doping

Transport direction:  1 1 1

Confinement direction in y:  -1 1 0

Confinement direction in z:  -1 -1 2

Cross-section of the nanowire with transport direction, [111]

Tool located at:

<https://nanohub.org/resources/omenwire>

# Optimized Nanowire Quantum Transport (Id-Vg Curve)

Id - Vg Curve with 1.9nm Cross Section & 5nm Channel/Gate Lengths

# Optimized Nanowire Quantum Transport (Critical Parameters)

# Hole Nanowire Bandstructure (Inputs)

All default settings were utilized, except as where shown:

1 Device Type → 2 Physics → 3 K-Space → 4 Numerics → 5 Simulate

Geometry: Nanowire (1D-periodic)

Calculation For: Electrons

Material: Si

Alloy Model: Virtual Crystal Approximation

Molar fraction: 0.5

Job Type: Calculate the wire band structure

Device cross section: Circle

Diameter: 8nm

Oxide Thickness( $Tox$ ): 2.2nm

Crystal Orientation

Transport direction (X): (100)

Confinement direction (Z): [010]

1 Device Type → 2 Physics → 3 K-Space → 4 Numerics → 5 Simulate

Electronic Structure | Strain |

Tight Binding Model:  $sp3d5s^*$

Spin-Orbit Coupling:  no

Dangling Bond Energy: 30eV

Explore: Valence bands

Electronic Structure | Strain |

Strain type: Uniaxial (along transport direction X)

Epsilon: 0.02

1 Device Type → 2 Physics → 3 K-Space → 4 Numerics → 5 Simulate

Number of k-points: 10

Number of bands: 10

Manual simulation venue selection:  no

Simulation Venue: nanoHUB.org (local)

Tool located at:

<https://nanohub.org/resources/bandstrlab>

# Resources

- [1] W. contributors, "Work function," Wikipedia, The Free Encyclopedia., 8 February 2024. [Online]. Available: [https://en.wikipedia.org/w/index.php?title=Work\\_function&oldid=1205050597](https://en.wikipedia.org/w/index.php?title=Work_function&oldid=1205050597). [Accessed 28 April 2024].

- [2] W. Lee, Y. Hwangbo, J.-H. Kim, and J.-H. Ahn, "Mobility enhancement of strained Si transistors by transfer printing on plastic substrates," *NPG Asia Materials*, vol. 8, no. 3, pp. e256–e256, Mar. 2016, doi: <https://doi.org/10.1038/am.2016.31>.

- [3] "Strained Transistors - REFERENCE PMOS-strained," [www.intel.com](http://www.intel.com).

[https://www.intel.com/pressroom/kits/advancedtech/doodle/ref\\_strain/strain.htm](https://www.intel.com/pressroom/kits/advancedtech/doodle/ref_strain/strain.htm)

- [4] Y. Chen *et al.*, "Mobility Enhancement of Strained MoS<sub>2</sub> Transistor on Flat Substrate," *ACS nano*, vol. 17, no. 15, pp. 14954–14962, Jul. 2023, doi: <https://doi.org/10.1021/acsnano.3c03626>.

- [5] K. Mistry *et al.*, "Delaying forever: Uniaxial strained silicon transistors in a 90nm CMOS technology," *IEEE Xplore*, Jun. 01, 2004. <https://ieeexplore.ieee.org/document/1345387>